*DATA SHEET*

# 数 据 手 册

BS10068

8Bit 60MSPS 低功耗 ADC

2025. 7

| BS10068          |      |                    |      |                                          |

|------------------|------|--------------------|------|------------------------------------------|

| 8 位 60Msps 模数转换器 |      |                    |      |                                          |

| 版本号: V1.03       |      | 当前版本时间: 2025 年 7 月 |      |                                          |

| 新旧版本改动比较:        |      |                    |      |                                          |

| 旧版               | 文档页数 | 当前版本               | 文档页数 | 主题 (和旧版本相比的主要变化)                         |

| V1.00            | 19   | V1.01              | 19   | 总谐波失真变大、输入电容变大、参考电阻调大、时序调整、输出驱动电压随输出电流变低 |

| V1.01            | 19   | V1.02              | 19   | 最大电压调低, 储存温度范围调小、增加输入共模偏差                |

| V1.02            | 19   | V1.03              | 19   | 更改 PD 恢复时间、更改图 10 输入外围电路图                |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

|                  |      |                    |      |                                          |

如果您有技术、交付或价格方面的任何问题, 请联系成都博思微科技有限公司的相关办公室或当地的代理商, 谢谢!

编制时间: 2025 年 7 月

## 产品概述

BS10068 是一款工作电压为 3V 的单芯片 8Bit 低功耗模数转换器, 内置片上采样保持电路, 转换速率最高为 70Msps。

出色的功耗表现, 实现每 MHz 频率仅消耗 1.15mW。在典型应用下, 60MSPS 仅消耗 69mW。该芯片具有低功耗模式, 通过拉高 PD 引脚的电平即可使芯片工作于低功耗模式, 在该模式下仅大约消耗 1mW。

在 25MHz 下的输入频率可达到 7.2 个有效位。具有较宽的参考电压调整范围, 同时也支持由外部接入, 还有 latch-up 和防输出短路的功能。数字输出采用 TTL/CMOS 兼容的独立输出电源引脚, 支持 3V 或者 2.5V 的逻辑电压的接口。BS10068 采用 24 引线的 TSSOP 封装。

## 产品特性

- 单电源供电(3V)

- 功耗 60Msps:69mW

低功耗模式: 1mW

- 单端输入

- 片上采样保持电路

- ENOB( $f_{in}=25\text{MHz}$ ): 7.2 bits

- THD( $f_{in}=25\text{MHz}$ ): -53 dB

## 应用领域

- 数字影像系统

- 机顶盒

- 便携式设备

- 激光测距

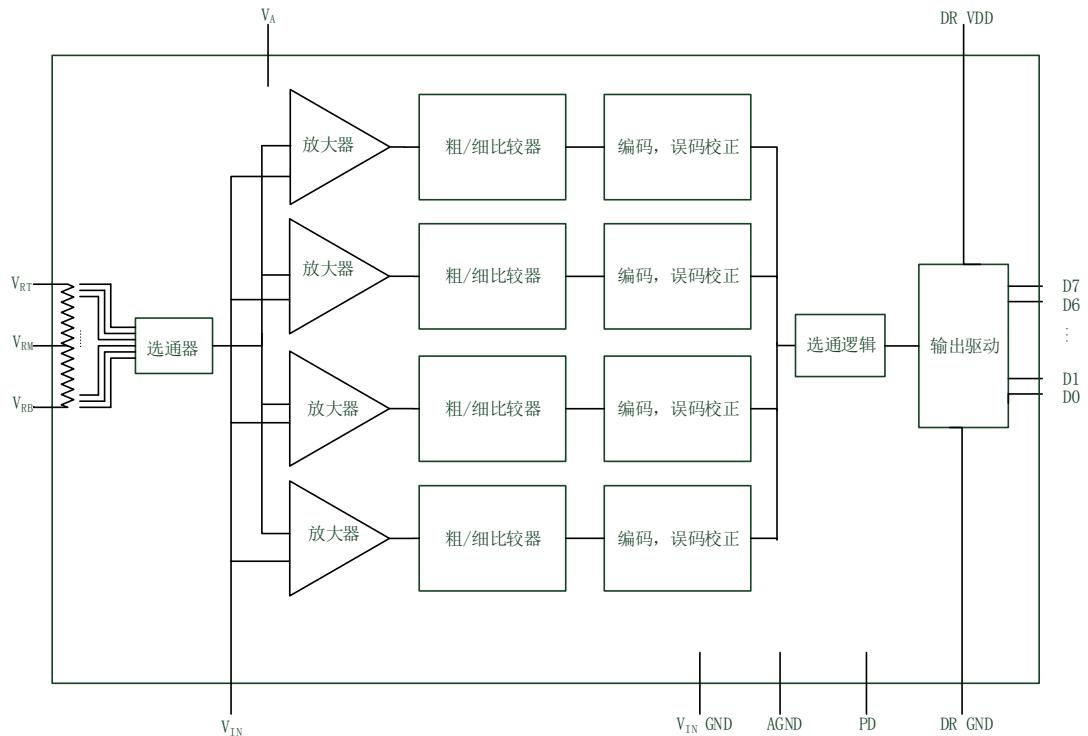

图 1 BS10068 示意图

## 目 录

|                         |    |

|-------------------------|----|

| 1 引脚描述 .....            | 1  |

| 1.1 引脚布局图 .....         | 1  |

| 1.2 引脚功能说明 .....        | 1  |

| 2 电特性 .....             | 2  |

| 2.1 电性能参数 .....         | 2  |

| 2.1.1 数字接口特性 .....      | 3  |

| 2.2 ESD 性能 .....        | 3  |

| 2.3 绝对最大额定值 .....       | 4  |

| 2.4 推荐工作条件 .....        | 4  |

| 2.5 典型性能特性（需测试结果） ..... | 4  |

| 3 功能特性 .....            | 5  |

| 3.1 功能概述 .....          | 5  |

| 3.2 典型应用概述 .....        | 6  |

| 3.3 端口描述 .....          | 10 |

| 3.3.1 电源电压 .....        | 10 |

| 3.3.2 PD 和时钟 .....      | 11 |

| 4 布局和接地 .....           | 11 |

| 5 常见应用的注意事项 .....       | 12 |

| 6 封装信息 .....            | 12 |

## 1 引脚描述

### 1.1 引脚布局图

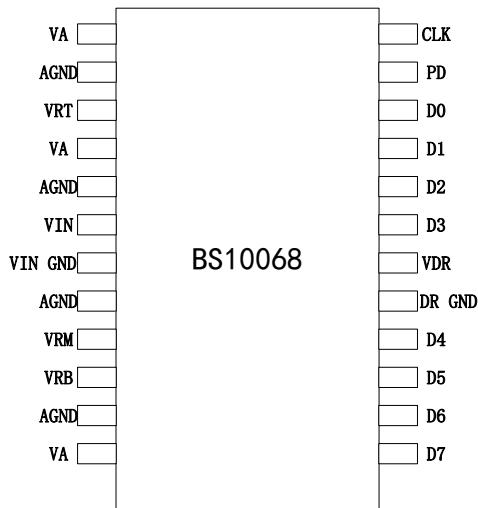

图 2 芯片管脚示意顶视图

### 1.2 引脚功能说明

表 1 引脚说明表

| 引脚序号          | 引脚名                 | 引脚类型 | 说明                                                                              |

|---------------|---------------------|------|---------------------------------------------------------------------------------|

| 1、4、12        | VA                  | 模拟电源 | 模拟电源                                                                            |

| 2、5、8、11      | AGND                | 模拟地  | 模拟电源地                                                                           |

| 3             | VRT                 | 输入   | 顶端参考输入，该参考电压决定了 ADC 转换的最高电压，超过该电压的模拟输入会被转换输出为全“1”，VRT 与 VRB 共同决定了 ADC 的转换输入电压范围 |

| 6             | V <sub>IN</sub>     | 输入   | 单端模拟输入                                                                          |

| 7             | V <sub>IN_GND</sub> | 电源   | 模拟输入参考地                                                                         |

| 9             | VRM                 | 输入   | 基准电压的中点，该管脚需要通过一个 0.1uF 的电容旁路到模拟地平面                                             |

| 10            | VRB                 | 输入   | 底端参考输入，该参考电压决定了 ADC 转换的最低电压，低于该电压的模拟输入会被转换输出为全“0”，VRT 与 VRB 共同决定了 ADC 的转换输入电压范围 |

| 13~16 及 19~22 | D7~D0               | 输出   | 转换输出数字接口                                                                        |

| 17            | DR_GND              | 数字地  | 数字地                                                                             |

| 18            | VDR                 | 数字电源 | 数字电源输入                                                                          |

| 23            | PD                  | 输入   | 功耗控制管脚，在该管脚上输入高电平后，会导致芯片进入低功耗模式；当在该管脚上输入低电平后，芯片进入正常工作模式。                        |

| 24            | CLK                 | 输入   | 时钟信号。CMOS/TTL 兼容的数字时钟输入。VIN 输入的模拟信号在该时钟上升沿被采样。                                  |

## 2 电特性

### 2.1 电性能参数

典型值的测量条件：环境温度为 25°C，VA 管脚电压为 2.7V~3.3V；VDR 管脚电压为 2.4V~3.3V；时钟频率为 60MHz；最小值、最大值包括了：环境温度-40°C~85°C 和推荐的工作电压。部分电参数测试条件（不同的电压和温度），标注在测试条件一栏。

表 2 电特性参数表

| 特性      | 符号                  | 条件：<br>除另有规定外，电源 VA=2.7V~3.3V，-40°C ≤ TA ≤ 85°C | 极限值及典型值 |      |             | 单位   |

|---------|---------------------|-------------------------------------------------|---------|------|-------------|------|

|         |                     |                                                 | 最小      | 典型值  | 最大          |      |

| 积分非线性   | INL                 |                                                 | -1.5    | ±0.7 | 1.5         | LSB  |

| 微分非线性   | DNL                 |                                                 | -0.9    | ±0.5 | 1.0         | LSB  |

| 误码      | MISSING COED        |                                                 |         | 0    |             |      |

| 满偏误差    | FSE                 |                                                 | -34     | ±22  | 34          | mV   |

| 0 点失调偏差 | ZSE                 |                                                 | -37     | ±21  | 37          | mV   |

| 输入电压    | V <sub>IN</sub>     |                                                 | VRB     | 1.6  | VRT         | V    |

| 输入电容    | C <sub>IN1</sub>    | 时钟低                                             |         |      | 7           | pF   |

| 输入电容    | C <sub>IN2</sub>    | 时钟高                                             |         |      | 8           | pF   |

| 输入电阻    | R <sub>IN</sub>     |                                                 | 1       |      |             | MΩ   |

| 输入全功率带宽 | BW                  |                                                 | 200     |      |             | MHz  |

| 参考电压顶   | V <sub>RT</sub>     |                                                 | 1.0     | 1.9  | VA          | V    |

| 参考电压底   | V <sub>RB</sub>     |                                                 | 0       | 0.3  | VRT-1<br>.0 | V    |

| 参考电压    | V <sub>RT-VRB</sub> |                                                 | 1.0     | 1.6  | 2.0         | V    |

| 参考电阻串   | R <sub>REF</sub>    |                                                 | 300     | 330  | 350         | Ω    |

| 参考电阻串电流 | I <sub>REF</sub>    |                                                 | 2.8     | 4.8  | 6.7         | mA   |

| 输入逻辑高电压 | V <sub>IH</sub>     |                                                 | 2.0     |      |             | V    |

| 输入逻辑低电压 | V <sub>IL</sub>     |                                                 |         |      | 0.8         | V    |

| 输入逻辑高电流 | I <sub>IH</sub>     |                                                 | 10      |      |             | nA   |

| 输入逻辑低电流 | I <sub>IL</sub>     |                                                 | -50     |      |             | nA   |

| 逻辑输入电容  | C <sub>IN</sub>     |                                                 | 3       |      |             | pF   |

| 有效位     | ENOB                | fin=2.3MHz, VIN=-0.25dBFS                       |         | 7.3  |             | Bits |

|         |                     | fin=24.7MHz, VIN=-0.25dBFS                      |         | 7.2  |             | Bits |

| 信号噪声谐波比 | SINAD               | fin=2.3MHz, VIN=-0.25dBFS                       |         | 46   |             | dB   |

|         |                     | fin=24.7MHz, VIN=-0.25dBFS                      |         | 45   |             | dB   |

| 信号噪声比   | SNR                 | fin=2.3MHz, VIN=-0.25dBFS                       |         | 46   |             | dBc  |

|         |                     | fin=24.7MHz, VIN=-0.25dBFS                      |         | 45   |             | dBc  |

| 无杂散动态范围 | SFDR                | fin=2.3MHz, VIN=-0.25dBFS                       |         | 60   |             | dBc  |

|         |                     | fin=24.7MHz, VIN=-0.25dBFS                      |         | 58   |             | dBc  |

| 总谐波失真   | THD                 | fin=2.3MHz, VIN=-0.25dBFS                       |         | -54  |             | dBc  |

|         |                     | fin=24.7MHz, VIN=-0.25dBFS                      |         | -53  |             | dBc  |

| 特性      | 符号           | 条件:<br>除另有规定外, 电源 $V_A=2.7V \sim 3.3V$ , $-40^\circ C \leq T_A \leq 85^\circ C$ | 极限值及典型值 |      |    | 单位            |

|---------|--------------|---------------------------------------------------------------------------------|---------|------|----|---------------|

|         |              |                                                                                 | 最小      | 典型值  | 最大 |               |

| 模拟电源电流  | $I_A$        |                                                                                 |         | 22.7 |    | mA            |

| 输出驱动电流  | DR ID        | 直流输入                                                                            |         | 0.2  |    | mA            |

|         |              | $f_{in}=2.3MHz$                                                                 |         | 4.2  |    | mA            |

| 总电流     | IA+ DR<br>ID | 直流输入, PD 拉低                                                                     |         | 22.9 |    | mA            |

|         |              | 直流输入, PD 拉高                                                                     |         | 0.3  |    | mA            |

| 总功耗     | $P_W$        | 直流输入, PD 拉低                                                                     |         | 69   |    | mW            |

|         |              | 直流输入, PD 拉高                                                                     |         | 1    |    | mW            |

| 最大转换速率  | $f_{cl}$     |                                                                                 |         |      | 70 | MSPS          |

| 最小转换速率  | $f_{c2}$     |                                                                                 | 20      |      |    | MSPS          |

| 最小时钟低电平 | $t_{cl}$     |                                                                                 | 4.5     |      |    | ns            |

| 最小时钟高电平 | $t_{ch}$     |                                                                                 | 4.5     |      |    | ns            |

| 输出保持时间  | $t_{oh}$     |                                                                                 |         | 10   |    | ns            |

| 输出延迟    | $t_{od}$     |                                                                                 |         | 26   |    | ns            |

| 输出流水延迟  | $t_{pd}$     |                                                                                 |         | 2.5  |    | Clk<br>cycles |

| 采样延迟    | $t_{ad}$     |                                                                                 |         | 1.5  |    | ns            |

| 孔径抖动    | $t_{aj}$     |                                                                                 |         | 2    |    | ps rms        |

## 2.2 数字接口特性

典型值的测量条件: 环境温度为  $25^\circ C$ ,  $V_A$  管脚电压为  $3V$ ;  $V_{DR}$  管脚电压为  $3V$ ; 最小值、最大值包括了: 环境温度  $-40^\circ C \sim 85^\circ C$  和推荐的工作电压。部分电参数测试条件 (不同的电压和温度), 标注在测试条件一栏。

表 3 数字接口特性参数表

| 特性              | 符号       | 条件: $V_{DR}=3V$ $V_A=3V$<br>除另有规定外, $T_A=$ 常温 ( $25^\circ C$ ) | 极限值  |    |     | 单位 |

|-----------------|----------|----------------------------------------------------------------|------|----|-----|----|

|                 |          |                                                                | 最小   | 典型 | 最大  |    |

| 逻辑输入高           | $V_{IH}$ |                                                                | 2.0  |    |     | V  |

| 逻辑输入低           | $V_{IL}$ |                                                                |      |    | 0.8 | V  |

| $DRV_{DR}=3V$   |          |                                                                |      |    |     |    |

| 输出逻辑高           | $V_{OH}$ | $V_{DR}=3V$ $I_{OH}=1.6mA$                                     | 2.7  |    |     | V  |

| 输出逻辑低           | $V_{OL}$ | $V_{DR}=3V$ $I_{OL}=1.0mA$                                     |      |    | 0.2 | V  |

| $DRV_{DD}=2.5V$ |          |                                                                |      |    |     |    |

| 输出逻辑高           | $V_{OH}$ | $V_{DR}=3V$ $I_{OH}=1.6mA$                                     | 2.35 |    |     | V  |

| 输出逻辑低           | $V_{OL}$ | $V_{DR}=3V$ $I_{OL}=1.0mA$                                     |      |    | 0.2 | V  |

## 2.3 ESD 性能

表 4 ESD 特性参数表

|                                                                       | ESD 模型 | 耐压值        | 单位 |

|-----------------------------------------------------------------------|--------|------------|----|

| V (ESD)                                                               | 人体模式 1 | $\pm 2000$ | V  |

| 注: JEDEC 的标准 JEP155 规定: HBM ESD 能力达到 500-V 就可以允许安全生产, 在标准的 ESD 控制流程中。 |        |            |    |

## 2.4 绝对最大额定值

绝对最大额定值如下：

- a) I/O 电源电压 ( $V_{DR}$ ):  $V_A+0.3V$ ;

- b) 电源电压 ( $V_A$ ): 3.6V;

- c) 结温 ( $T_J$ ): 120°C;

- d) 引线耐焊接温度 ( $T_h$ ) (4s): 235°C;

- e) 功耗 ( $P_D$ ): 1mW;

- f) 热阻 ( $R_{\theta Jc}$ ): 20°C/W;

- g) 贮存环境温度 ( $T_{stg}$ ): -55°C ~ 125°C;

- h) 静电放电敏感度 ( $V_{ESD}$ ): 2000V (HBM)。

## 2.5 推荐工作条件

推荐工作条件如下：

- a) I/O 电源电压 ( $V_{DR}$ ): 2.4V ~ VA

- b) 电源电压 ( $V_A$ ): 2.7V ~ 3.6V;

- c) 输入高电平电压 ( $V_{IH}$ ): 2.0V ~  $V_{DR}$ ;

- d) 输入低电平电压 ( $V_{IL}$ ): GND ~ 0.8V;

- e) 时钟频率 ( $f_{CLK}$ ): 20MHz ~ 60MHz;

- f) 工作温度 ( $T_A$ ): -40°C ~ 85°C。

## 2.6 典型性能特性

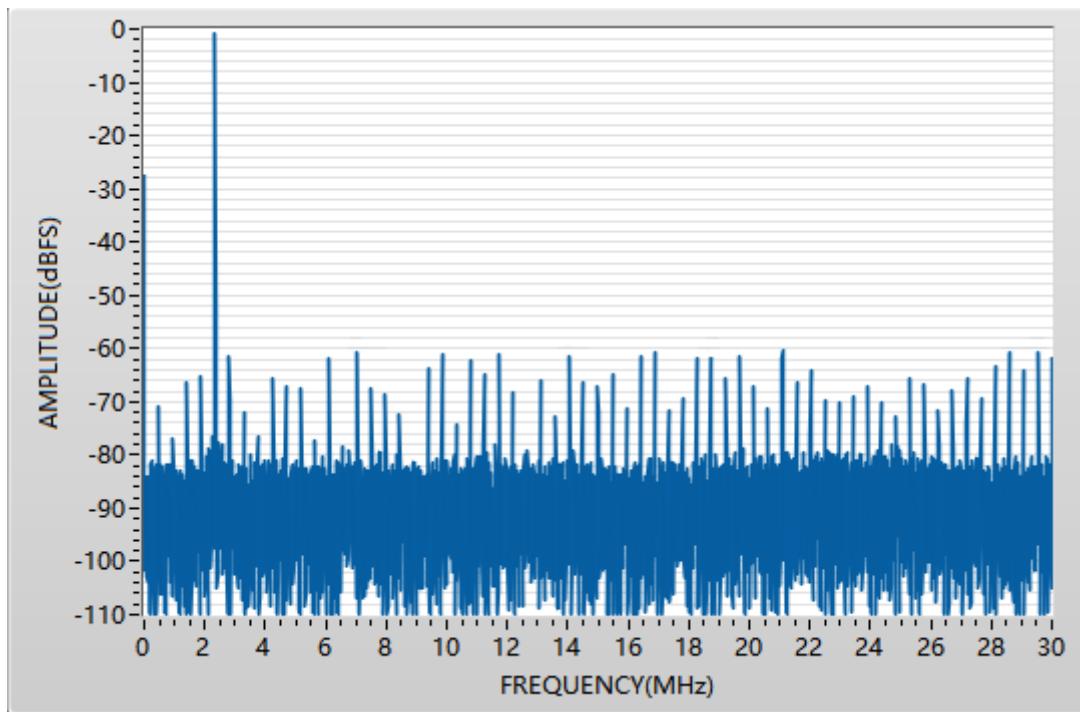

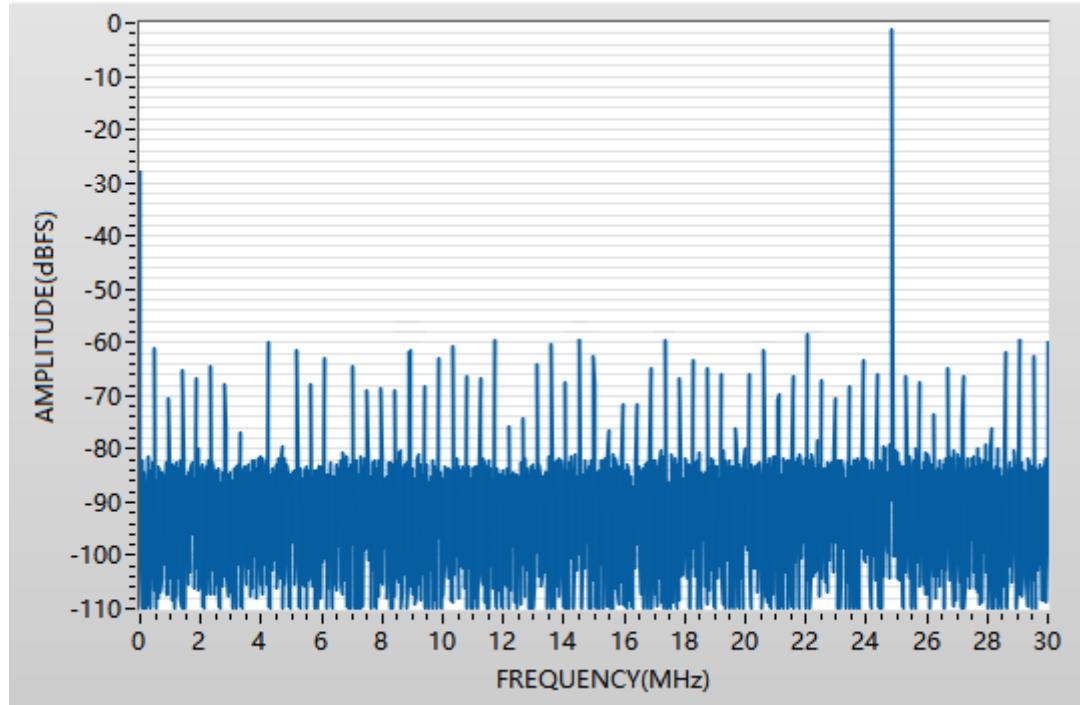

除非另有说明，否则所示测试都是在  $V_A=3V$ 、 $V_{DR}=3V$ 、 $T_A=25^\circ C$ 、采样率为 60MHz 情况下进行测试所得到的数据。

图 3 FIN=2.3MHz FS=60MHz SNR=46dB SFDR=60dB VIN=-0.25dBFS

图 4 FIN=24.7MHz FS=60MHz SNR=45dB SFDR=58dB VIN=-0.25dBFS

### 3 功能特性

#### 3.1 功能概述

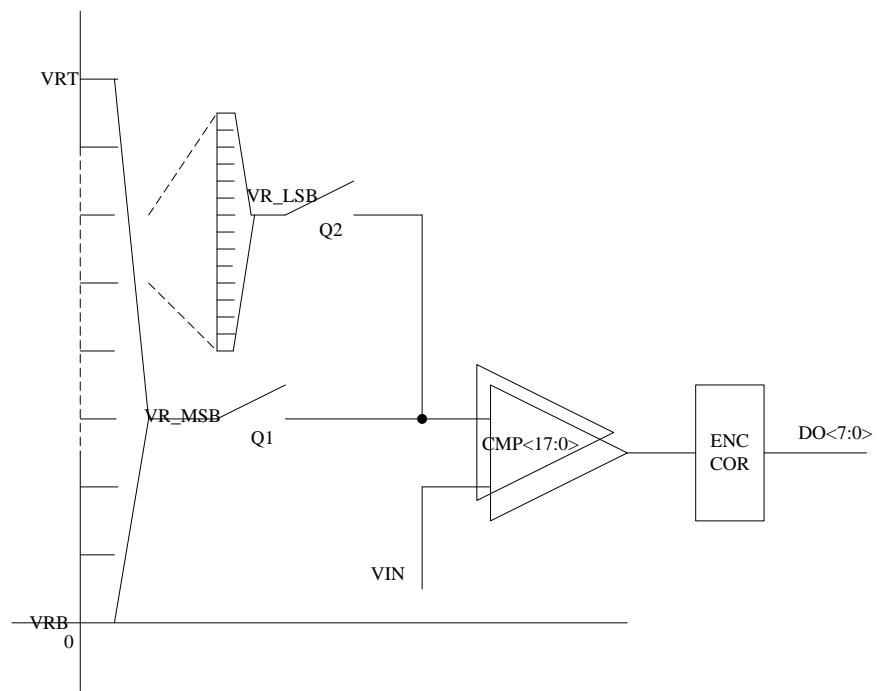

BS10068 是一款具有内部采样保持放大器的 8 位模数转换器，通过将输入信号先粗量化得到高位信号，在根据粗量化的结果进行细量化，最后经过数字编码输出 8 位数字信号。BS10068 可以在采样频率高达 60M Hz 下达到 7.2 bits 以上的有效位。当输入信号电压在 VRT 和 VRB 之

间的信号均可以转化成 8 位的数字信号，当输入信号低于 VRB 时，输出均为 0，当输入信号高于 VRT 时，输出均为 1。

采样时钟的下降沿时刻代表当次采样结束，数字数据的会在 2.5 个采样时钟周期加上  $t_{OD}$  以后输出，BS10068 将随着采样时钟一直输出二进制的数字码。

BS10068 具有 1 个 PD 管脚，用于支持功耗控制，当 PD 引脚为低时，设备处于正常工作状态；当 PD 引脚为高时，设备处于低功耗模式（断电模式）；输出引脚保持最后一次转换的结果在 PD 引脚变高之前，在该情况下只有 1.4mW 的功耗，保持时钟输入低将进一步将 PD 模式下的功耗降低为 1mW。

图 5 BS10068 原理框图

### 3.2 典型应用概述

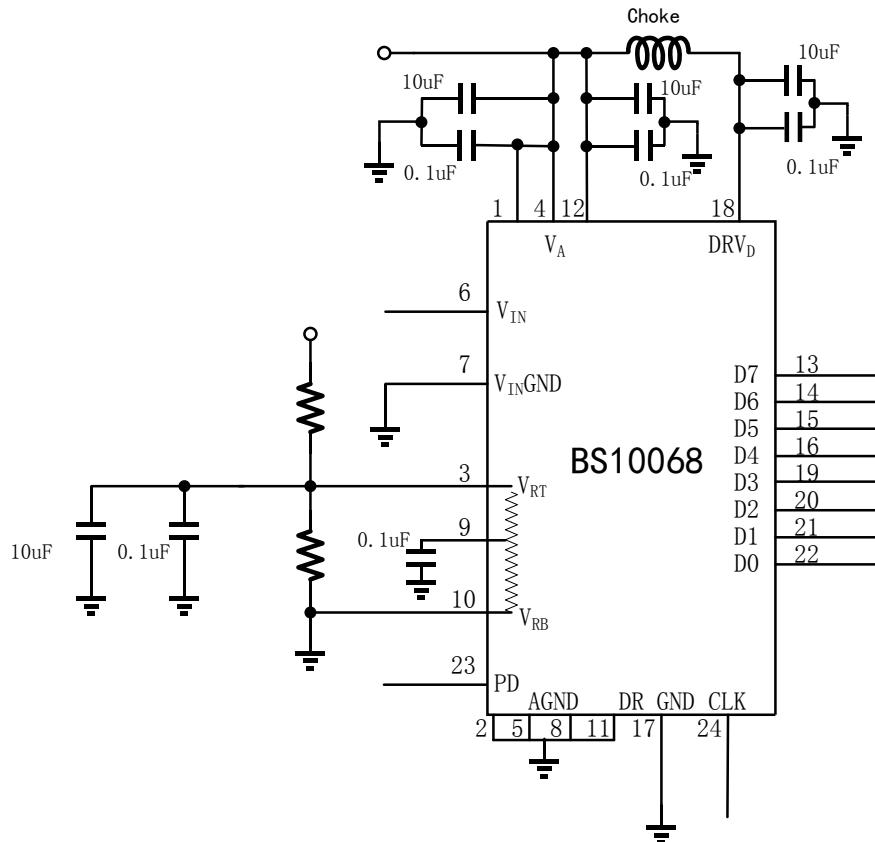

产品的典型应用电路如下图所示。

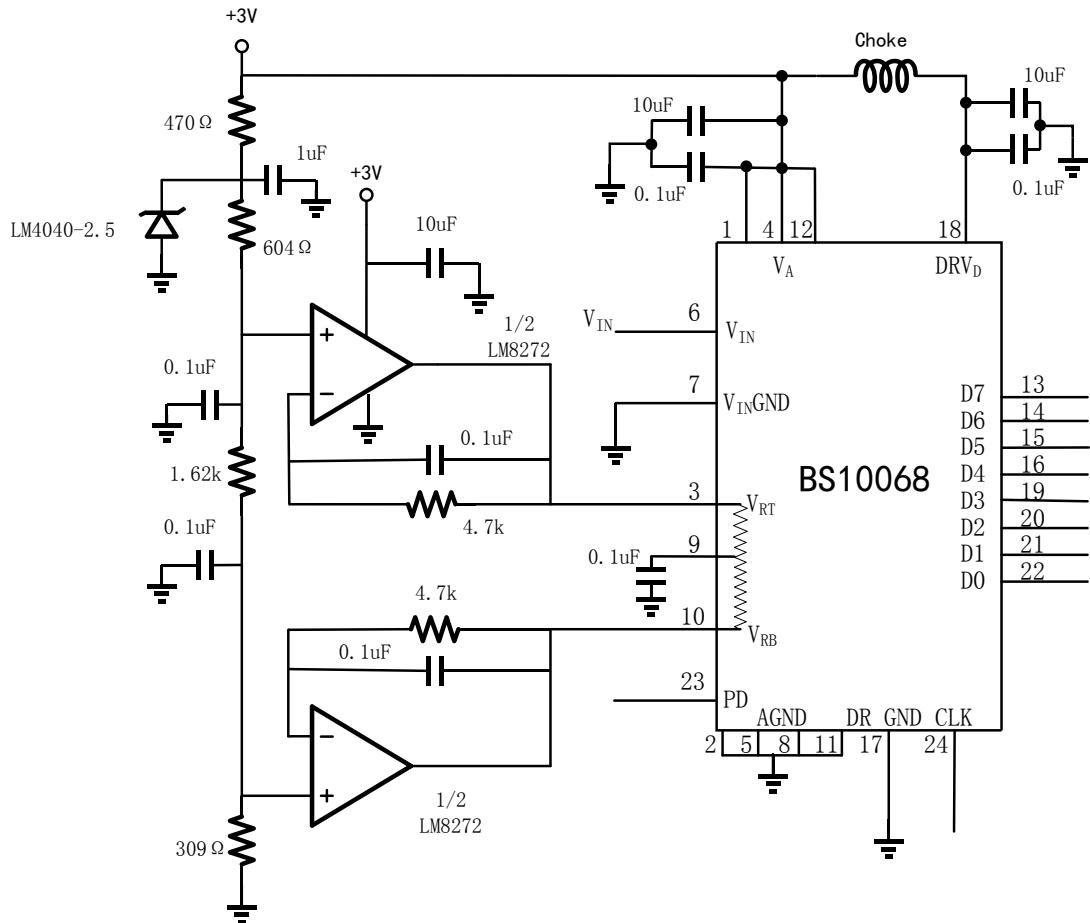

图 6 简单的参考电压产生电路图

图中,  $V_{RT}$  为参考电压顶部,  $V_{RB}$  为参考电压底部。当  $VIN$  管脚上的输入电压介于  $V_{RT}$  和  $V_{RB}$  之间时, 模拟输入电压会被转换成 8bit 的数字信号。

上图给出的参考电压偏置是非常简单的，但是所表现的性能可以满足大部分的应用需求，由于电路的负载越大将会导致参考电压的变化越大，而低阻抗的参考电压产生电路将会使参考电压越稳定。为使器件工作正常，工作环境及输入需严格按照前面给出的推荐工作条件，使用任何器件产生的参考电压都必须保证有足够的电流以保持参考电压的稳定。

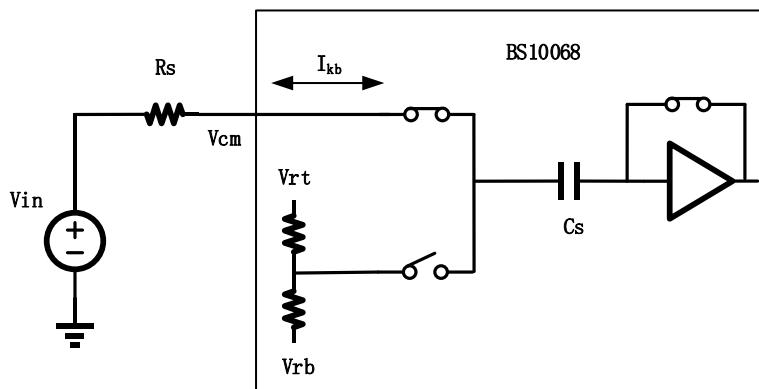

器件的 VIN 管脚可以支持直流耦合及交流耦合两种电压输入模式：

- a) 对于直流耦合输入，当输入信号的内阻过大时，会因芯片输入端存在的 kick back 电流造成输入直流电压偏差，原理如下图所示。

图 7 直流耦合输入电压偏差原理图

在产品应用设计过程中，应按如下公式计算产品的实际输入电压。

$$V_{cm} = V_{in} + R_s * I_{kb}$$

式中：

$V_{cm}$ -输入共模电压；

$V_{in}$ -输入电压

$R_s$ -输入电源内阻

$I_{kb}$ -kick back 电流

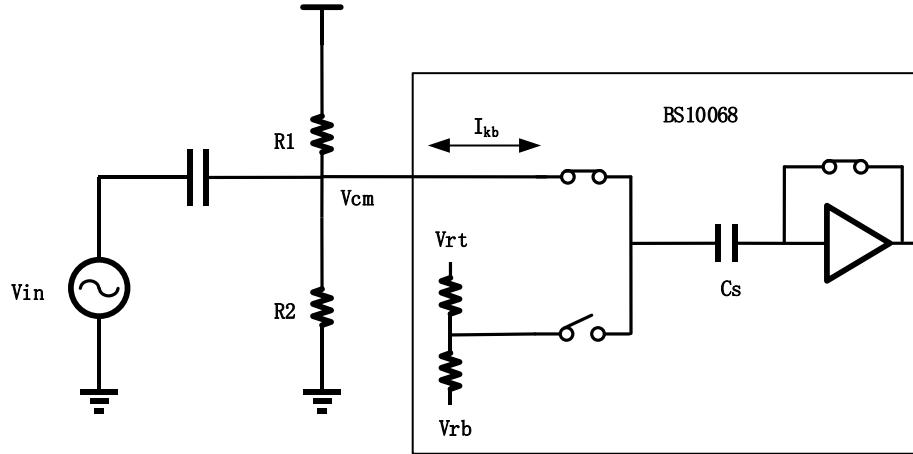

- b) 对于交流耦合输入，芯片输入端的存在的 kick back 电流也会造成直流点偏差，原理如下图所示。

图 8 交耦合输入电压偏差原理图

在产品应用设计过程中，应按如下公式计算产品的实际输入电压。

$$V_{cm} = \left( \frac{V_A}{R1 + R2} + I_{kb} \right) * R2$$

式中：

$V_{cm}$ -输入共模电压；

$V_A$ -输入电压

$R_s$ -输入电源内阻

$I_{kb}$ -kick back 电流

$R$ -分压电阻。

图 9 低阻抗参考电路示意图

上图所示的电路可以使参考电压表现出来更好的性能，参考顶的运放必须满足由  $V_{RT}-V_{RB}$  和参考电阻串所需要的电流驱动能力，同理，接参考底的运算放大器也要具有相同的电流能力，放大器接入的电容负载也需要满足环路的稳定性，选择 LM8272 这款放大器的原因是其轨到轨的输入结构和其输出具有很强的带载能力足以适应宽范围的输入共模并且可以驱动很大的电容负载。

输入部分的可调分压电阻可以适应更多不同参考的应用，当然也可以把这部分分压电阻电路替换成电位计或者 DAC 来精确的控制参考电压，当输入电压的最低部分为 0 时，参考底也可以直接接地。

参考顶的电压选择必须要高于参考底，并且  $V_{RT}-V_{RB}$  的选择范围需要按照前面的表格设置以减小噪声，当参考顶可能应用于输入为  $V_A$  的情形或者参考底应用于输入为 0 的情形， $V_{RT}-V_{RB}$  的值不能超过 2V 以避免波形失真。 $V_{RM}$  是参考顶和参考底的中间值，需要接 0.1uF 的电容旁路到地，这个 PIN 不能悬空或者有超过 10uA 的电流。

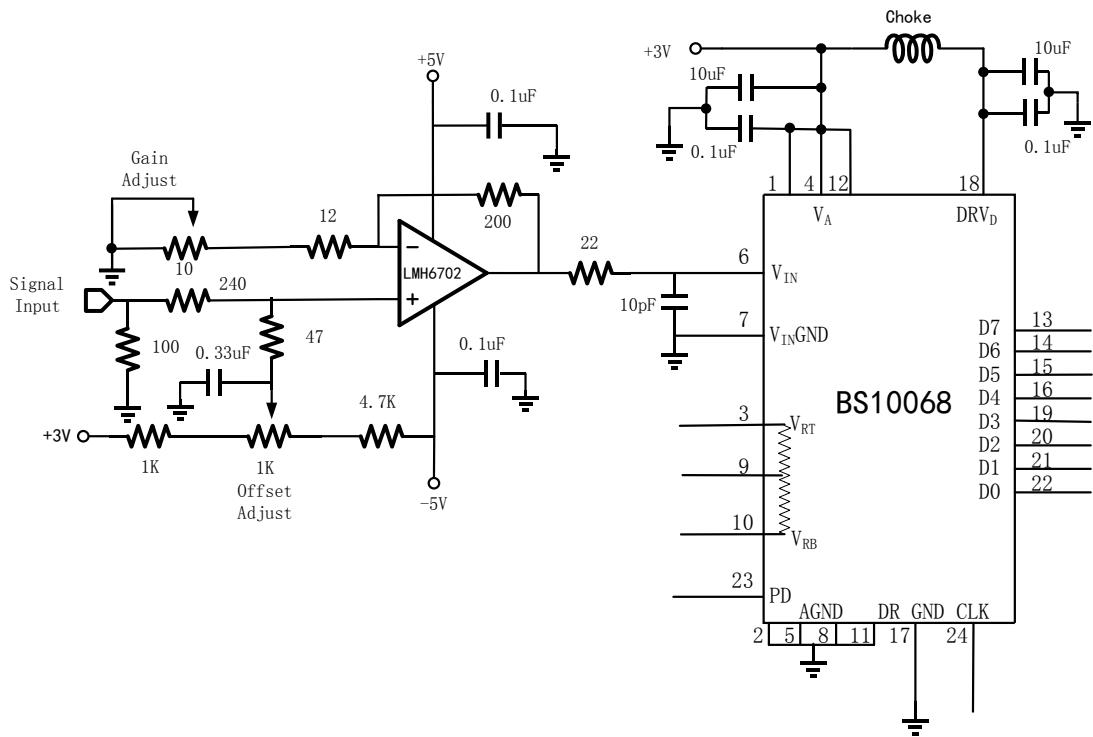

图 10 电路输入外围电路图

BS10068 的输入电路由可调的运算放大结构组成，输入电容的大小随着采样时钟的电平变化，当采样电平为低时，输入电容为 7pF，当采样电平为高时，输入电容为 8pF。当模拟输入端有电流毛刺时就会出现电压尖峰，但是用来驱动模拟输入端的电路必须要保证在采样时钟高电平时间内保持稳定，LMH6702 和 LMH6628 可以作为 BS10068 的模拟输入驱动放大器的。

模拟输入的时间常数最优值不仅取决于放大器和 ADC 电路，也和版图走线和焊接金属有关，电阻值的选取是在 18 到 47Ω 之间，电容根据下面的公式计算得知，

$$C = \frac{1}{2 \times \pi \times R \times F_{clk}},$$

这个电容值包含了采样时钟为高的输入电容，这个设置有助于优化电路的 SNR，当电容和电阻均为 0 时可以实现最佳的 THD，但是必须得和 SNR 和 SINAD 做折中，一般来说，对于欠采样应用是不需要加这个电容的。

上图中，模拟输入的驱动电路还集成了增益和 offset 调整，满偏误差也可以调整  $V_{RT}$  和  $V_{RB}$ ，但是这肯定需要用到 DAC 的调整。

### 3.3 端口描述

#### 3.3.1 电源电压

模数转换器工作时如果没有足够的旁路电容，足够的抽拉电流会恶化电源电压，一般会在电源引脚 2.5cm 内放置一个 10uF 的电解电容作为旁路电容，电源引脚之间也需要加上 0.1uF 的陶瓷电容，距离不超过 1cm。最好使用没有引脚的电容以减少引线电感。

对于 BS10068 来说，模拟电源  $V_A$  和  $V_{DR}$  最好使用单独的电源供电，并且做好隔离以防止数字噪声耦合到模拟端，一般会在这些电源端加上扼流线圈或者 27Ω 的电阻，并且在靠近电源端处要有足够的旁路电容，对于像 BS10068 类似的高速模数转换器来说，具有一定的电源抑制能

力, 任何与数字相关的电源都不能用于模拟端的电源, 模拟端的电源也一样。任何 PIN 都不能接入超过电源电压或者低于电源地 300mV, 即使是瞬态电压也不行, 这将会影响电源的开关, 电源的选取要确保电源有足够的驱动能力。

### 3.3.2 PD 和时钟

#### 3.3.2.1 PD

BS10068 具有 1 个 PD 管脚, 用于支持功耗控制, 当 PD 引脚为低时, 设备处于工作状态; 当 PD 引脚为高时, 设备处于低功耗模式 (断电模式); 输出引脚保持最后一次转换的结果在 PD 引脚变高之前, 在该个情况下只有 1.4mW 的功耗, 保持时钟输入低将进一步将 PD 模式下的功耗降低为 1mW。

#### 3.3.2.2 时钟

测试表明, BS10068 可以在采样频率 60M Hz 下保持很好的性能, 即使是在 20MHz~70MHz 的采样频率范围内, 依然可以提供完整的功能特性。停止掉时钟可以达到和拉高 PD 端一样的效果, 这个时候的功耗典型值只有 3mW。但是当时钟停止或者 pd 端被拉高以后, 数据输出端将需要 2us 的时间才会恢复有效, 因为功耗和时钟频率是保持线性关系的, 所以必须要等待时钟恢复或者改变时钟频率 2us 后, 该器件才能正常工作。

时钟信号的高电平和低电平时间会影响所有的 AD 转换器性能, 而要提供精确的 50% 占空比的时钟信号无疑是非常困难的, BS10068 的设计可以在较宽的时钟占空比范围内保持良好的性能。比如在 60M Hz 采样速率下, 占空比为 50% 时, BS10068 可以达到很好的性能。同时, 在时钟的高低电平分别为 4.5ns 时也可以保持高性能, 对应的 60M Hz 时钟的占空比就是 28% 到 72%。值得注意的是最低和最高占空比时钟是不能同时存在的。

当时钟线的长度超过如下公式所得到结果的长度时, 应该考虑走线的阻抗匹配。

$$\frac{t_r}{6 \times t_{prop}}$$

其中,  $t_r$  为时钟信号上升时间,  $t_{prop}$  为信号沿着走线的传输速率。典型情况下, 在 FR-4 板材中的  $t_{prop}$  值为 150ps/英寸或 59ps/厘米。

## 4 布局和接地

合理的布局和接地对于模数转换器的精确度是非常重要的, 数字噪声和模拟电路的耦合会对性能造成很大的影响, 并且很难补救, 因此最好保持所有的模拟和数字的走线都分离开, 并且彼此间保持大于 6 倍到参考平面的高度。

模数器件应该做好隔离, 数字驱动电源到地的通路与其他到地的通路不应该一样, 高压的数字器件不能放在模数转换器或者一系列的线性器件和电源之间, 因为这样会造成模数转换器的地波动。

一般来讲, 在高速系统中, 模数信号线应该垂直 90° 走线来避免信号走线之间的影响, 高频应用时, 即使是 90 度走线也应该避免, 因为即使一点信号的耦合也会影响性能。时钟线也应该独自走线, 模拟输入端应该远离有噪声的信号线以免在输入端引入毛刺, 任何外围器件包括连接输入和地之间的滤波电容都应该接入干净地。

为了达到前文所述的 BS10068 的性能, 输入时钟的 jitter 应该小于 2ps (rms), 输入时钟和到数字的时钟需要用足够多的 buffer 和时钟树隔离开。

## 5 常见应用的注意事项

**模拟输入端或者数字输入超压:** 正常操作下, 任何 pin 都不能超过电源电压或者低于电源地 300mV, 即使是瞬态电压也可能会损坏器件, 对于高速器件来说, 很难看到会有低于 1V 的的下冲电压, 一般来说, 在数字输入端加上 51 欧姆的电阻可以避免这个问题。对于 BS10068 来说, 超压使用可能会造成精度损失甚至损害器件。

**驱动高阻抗的数字总线:** 数字输出端的负载越大, 对于从数字电源到地的电流要求越高, 这样大电流可能就会耦合到模拟电路里面造成动态性能的下降, 如果驱动的负载超过 5pF, 最好在数字输出端加上 buffer 以增加驱动, 如果在数字输出端串上 47 到 56 欧姆的电阻也可以减少耦合到输入端的噪声使动态性能变好。

**模拟输入端的放大器不合格:** 模拟输入端的输入电容随时钟的输入从 7pF 到 8pF 变换, 因此, 在选择合适的放大器时应该考虑到变换的负载电容会比固定的电容更难驱动。

**参考电压源对电流的抽拉能力不足:** 前文提到的对  $V_{rt}$  和  $V_{rb}$  来说需要足够的抽拉电流能力, 否则  $V_{rt}$  和  $V_{rb}$  的不稳定将造成性能下降。

**时钟源的 jitter 过大, 时钟线过长, 时钟链路上有耦合:** 这将会造成采样周期间隔变化, 引起额外的输出噪声, 影响 SNR, 一般来讲, 有简单逻辑门驱动的 RC 时钟源都是不适合作为模数转换器的时钟源的。

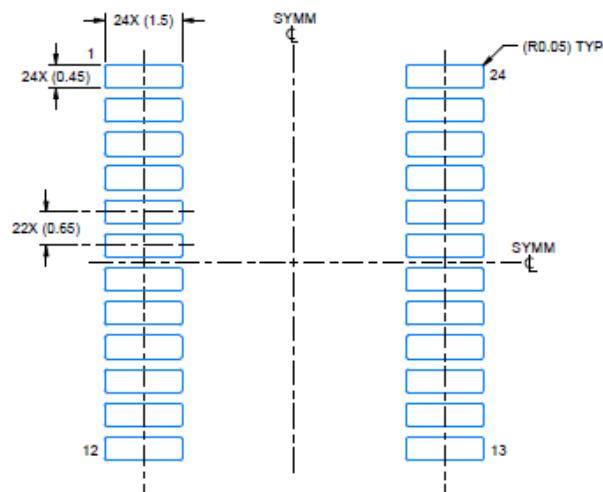

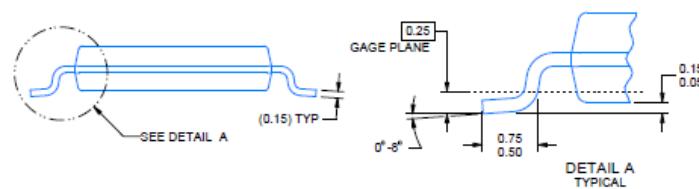

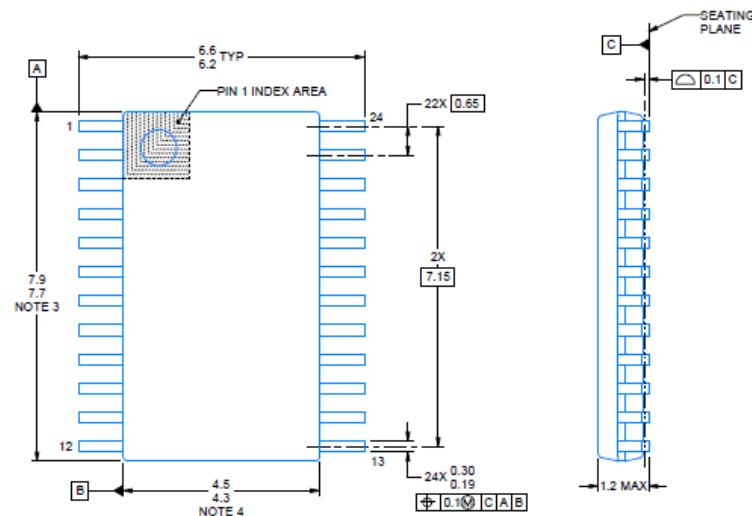

## 6 封装信息

表 5 封装参数表

| 器件      | 封装形式  | 封装配置 | 引脚数 | 标准包装数 | 长 (mm) | 宽 (mm) | 高 (mm) |

|---------|-------|------|-----|-------|--------|--------|--------|

| BS10068 | TSSOP | PW   | 24  | 2500  | 367.0  | 367.0  | 35.0   |

表 6 外壳外形参数表

单位为毫米

| 尺寸符号  | 数 值 |      |     |

|-------|-----|------|-----|

|       | 最 小 | 公 称  | 最 大 |

| $A_1$ |     | 7.15 |     |

| A     | 7.7 | 7.8  | 7.9 |

| B1    | 4.3 | 4.4  | 4.5 |

| B     | 6.2 | 6.4  | 6.6 |

| b     |     | 0.65 |     |

| c     |     | 0.2  |     |

| D     |     |      | 1.2 |

| e     |     | 0.1  |     |

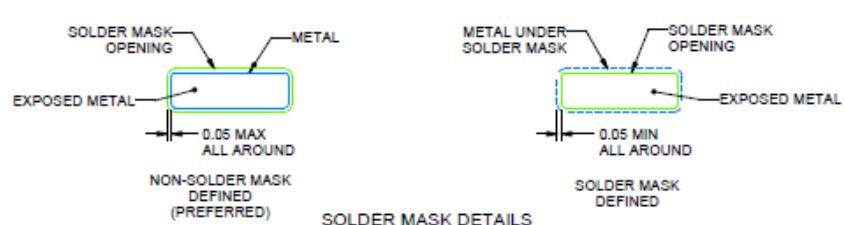

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

图 11 封装图