DATA SHEET

# 数 据 手 册

BS6302

3GHz 频率转换器

编制时间：2024 年 2 月

| BS6302<br>3G 频率转换器 |      |                    |      |                              |

|--------------------|------|--------------------|------|------------------------------|

| 版本号: V2.00         |      | 当前版本时间: 2024 年 2 月 |      |                              |

| 新旧版本改动比较:          |      |                    |      |                              |

| 旧版                 | 文档页数 | 当前版本               | 文档页数 | 主题 (和旧版本相比的主要变化)             |

| V1.00              | 49   | V2.00              | 52   | 按最新版本测试结果更新相关指标，并增加输入回波损耗指标。 |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

|                    |      |                    |      |                              |

如果您有技术、交付或价格方面的任何问题，请联系公司的相关办公室或当地的代理商，

谢谢！

编制时间: 2024 年 02 月

## 芯片特征:

- 参考输入频率,  $\leq 400\text{MHz}$

- 频率合成器频率范围:

30MHz~4000MHz

- 内部集成 VCO

$-123\text{dBc/Hz}@1\text{MHz}, 4\text{GHz}$

- 频率合成器带内相噪: -

$111\text{dBc/Hz}@100\text{kHz}, 1\text{GHz}$

- 高线性度 RF 混频器。

- 混频器频率范围:

30MHz~3700MHz

- 输入 IP3: +23dBm

- 低功耗模式 Mixer 偏置可调

- 支持两个 Mixer 同时工作全双工模式

- 电源电压 2.7V~3.3V

- 3 线或 4 线串口控制

- 内部集成高稳 ADC 参考基准源(可选外部输入)

## 应用领域:

- 有线电视前端

- 数字电视中继器

- 分集接收机

- 软件无线电

- 频带搬移

- 点到点无线通信

- 移动通信中继器干扰机

- WiMax/LTE 网络

- 卫星通信

- VHF/UHF 无线广播

## 产品概述:

这款芯片是一款可配置的频率转换器, 内部集成一个带 VCO 的频率合成器和 2 个高线性的混频器。频率合成器采用片外环路滤波器, 产生本振的频率范围是 30MHz~4000MHz。本振信号也可以通过外部输入缓冲后给 RF 混频器, 实现 30MHz~3700MHz 频率范围的上/下变频。混频器的偏置电流进行编程, 满足不同应用下的低功耗需求。混频器旁路模式下, 电路可作为独立的信号源。芯片通过三线串口进行的配置, 测试模式下可读出芯片内部状态信号。芯片工作电压 2.7V~3.3V, 采用 QFN32 封装, 工作温度范围-40°C~85°C。

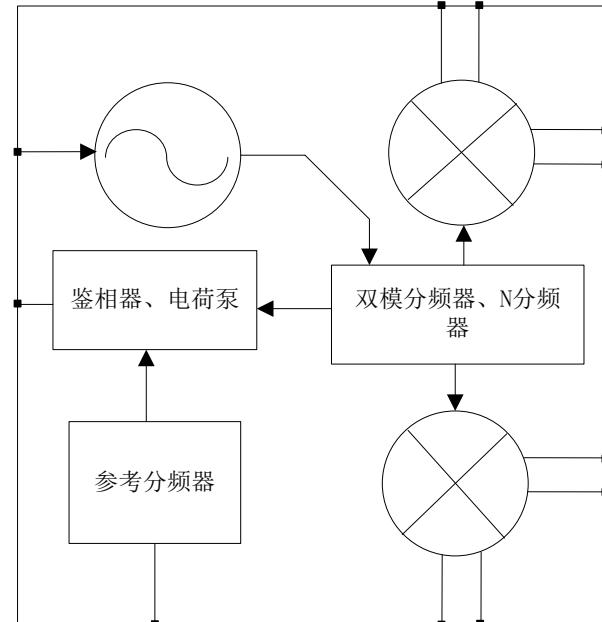

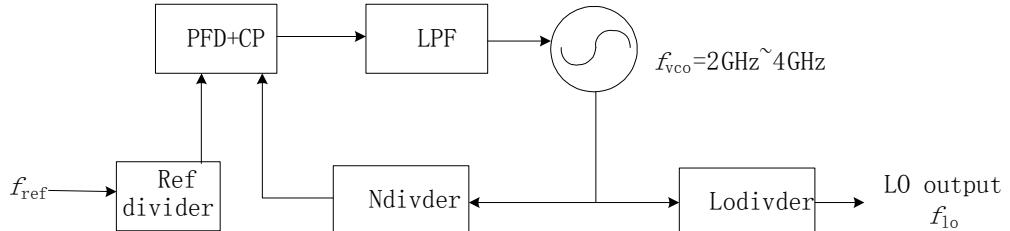

图 1 BS6302 功能框图

## 目 录

|                                   |    |

|-----------------------------------|----|

| 1. 引脚描述                           | 1  |

| 1.1 引脚布局图                         | 1  |

| 1.2 引脚功能说明                        | 1  |

| 2 参数规格                            | 2  |

| 2.1 绝对最大额定值                       | 2  |

| 2.2 参数                            | 2  |

| 3 工作原理                            | 3  |

| 3.1 功能框图                          | 3  |

| 3.2 参考输入                          | 4  |

| 3.3 鉴频鉴相器 PFD 和电荷泵 CHARGE PUMP 电路 | 5  |

| 3.4 分频器                           | 5  |

| 3.5 压控振荡器 LC VCO                  | 6  |

| 3.6 锁定检测电路                        | 7  |

| 3.7 宽频带混频器 MIXER                  | 8  |

| 3.8 串行接口                          | 9  |

| 3.9 硬件控制                          | 9  |

| 3.10 串行数据接口控制                     | 10 |

| 3.11 多片模式                         | 10 |

| 3.12 通用接口 GPO                     | 11 |

| 4 参数测试波形                          | 11 |

| 4.1 电源电流测试                        | 11 |

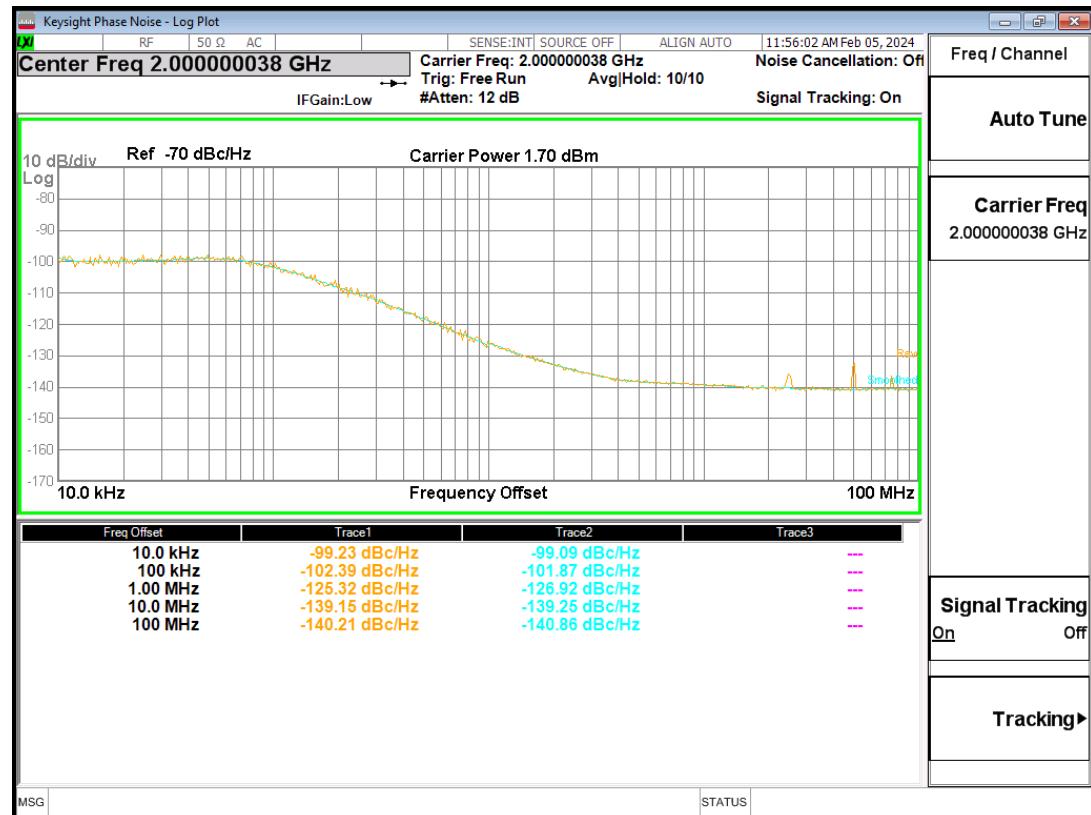

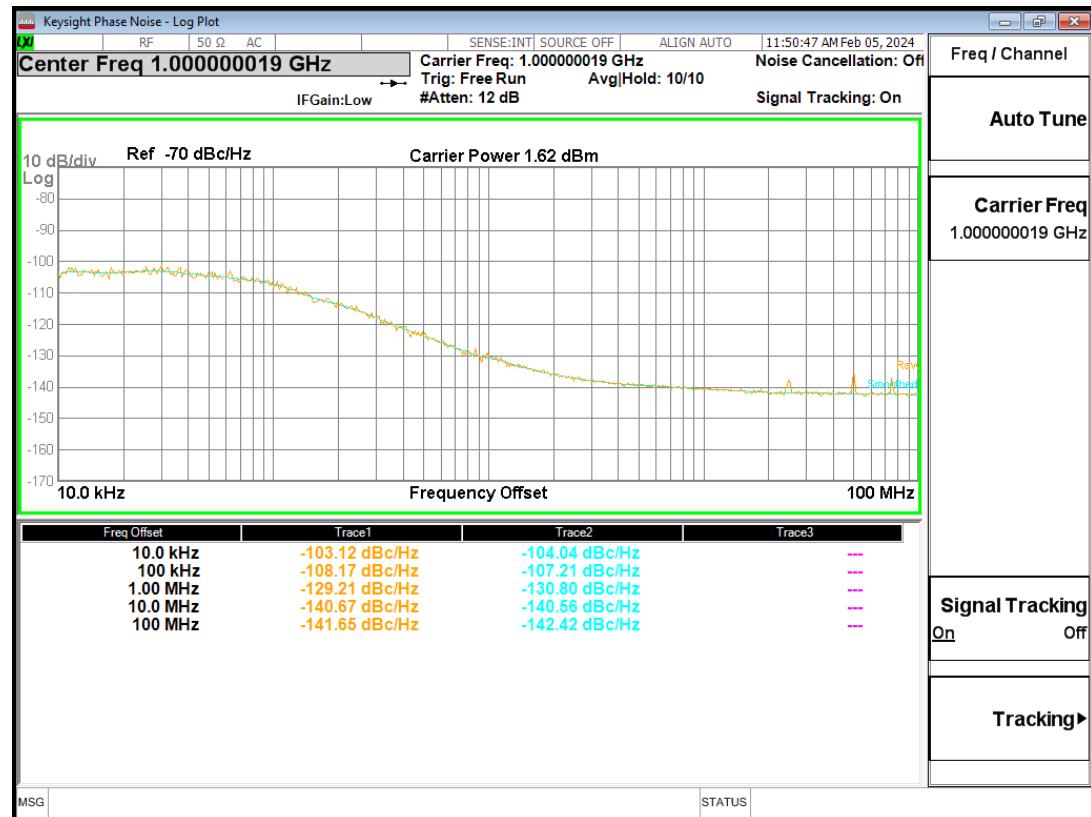

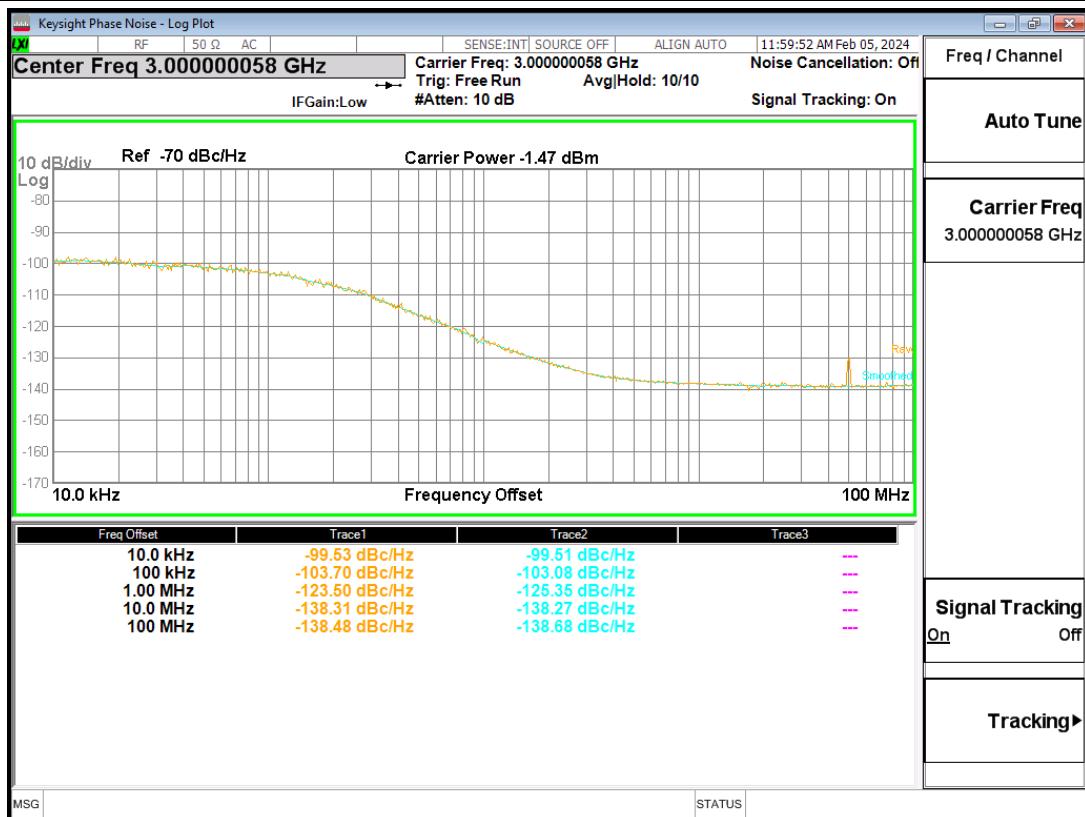

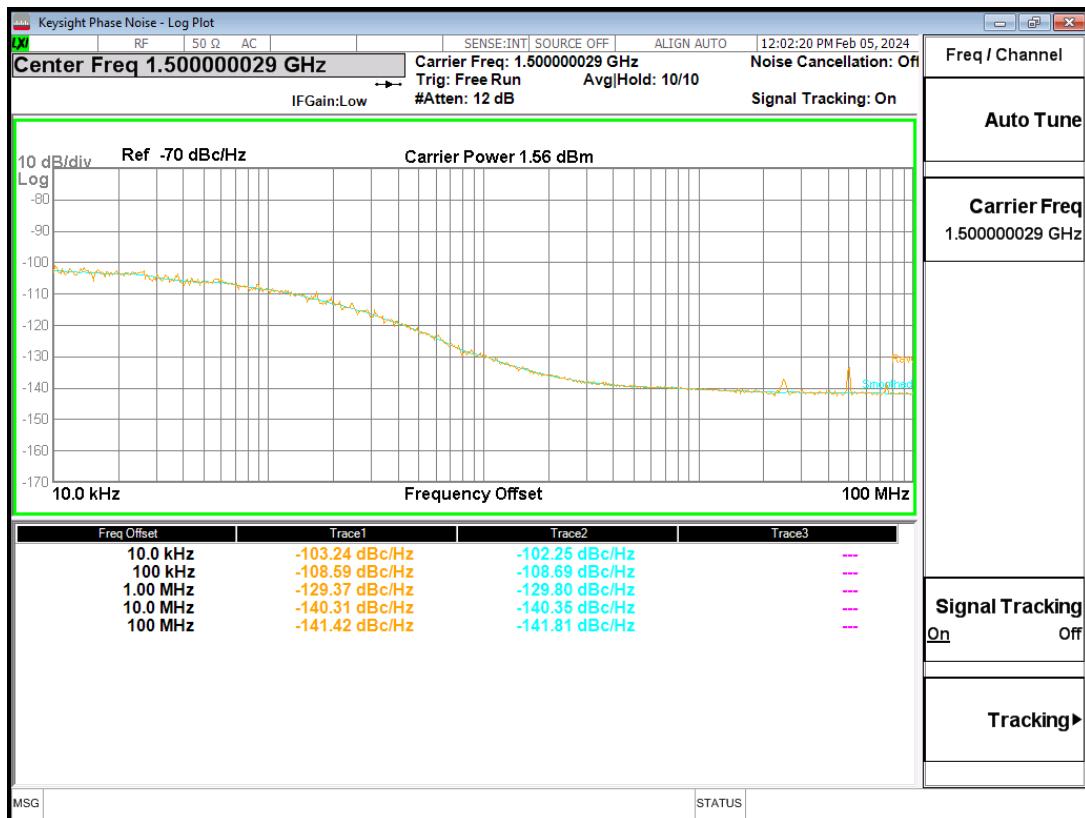

| 4.2 频率合成器的相位噪声测试                  | 12 |

| 4.2.1 鉴相频率为 50MHZ 时的测试            | 12 |

| 4.2.2 鉴相频率为 25MHZ 时的测试            | 15 |

| 4.3 VCO 的性能测试                     | 18 |

| 4.3.1 VCO 的频率范围测试                 | 18 |

| 4.3.2 VCO 的 KV 测试测试               | 19 |

| 4.3.3 VCO 的相位噪声测试                 | 22 |

| 4.4 MIXER 的性能测试                   | 25 |

| 4.4.1 转换增益 CONVERSION GAIN        | 25 |

| 4.4.2 三阶交调 IIP3                   | 26 |

| 4.4.3 本振 LO 和射频输入在 MIXER 输出口的泄露   | 28 |

| 4.4.4 混频器输入和输出端的输入回波损耗 (S11)      | 30 |

| 5 寄存器列表                           | 32 |

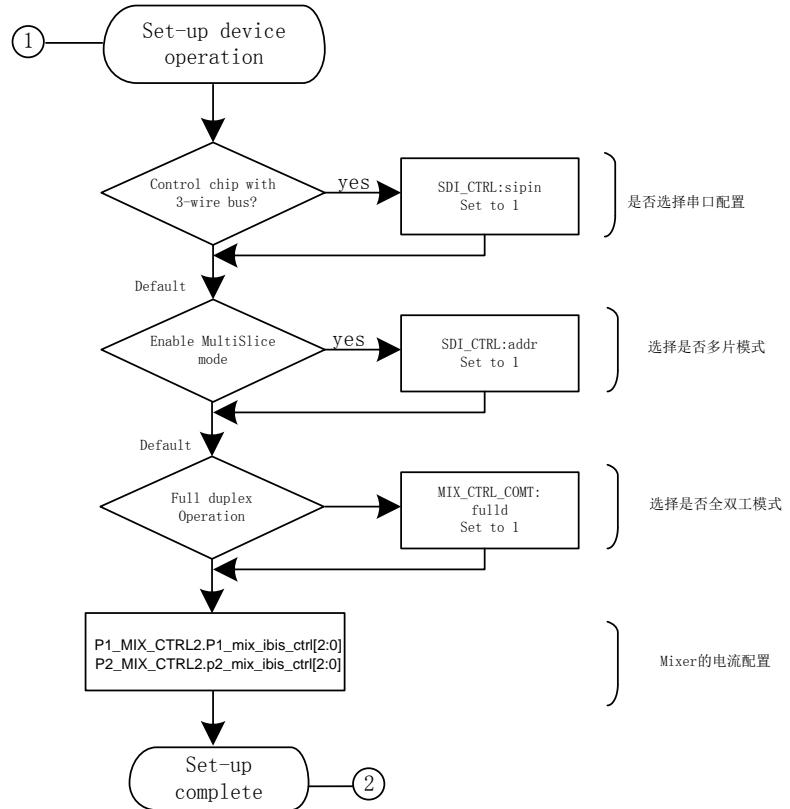

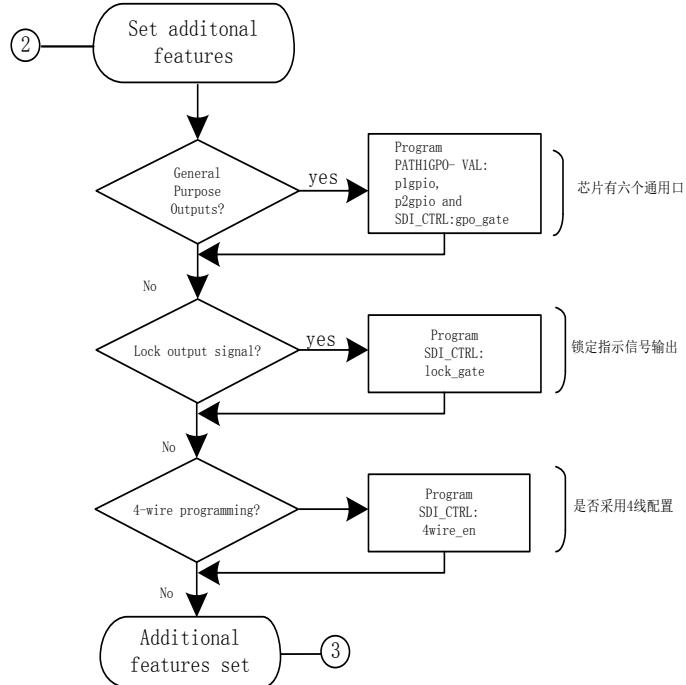

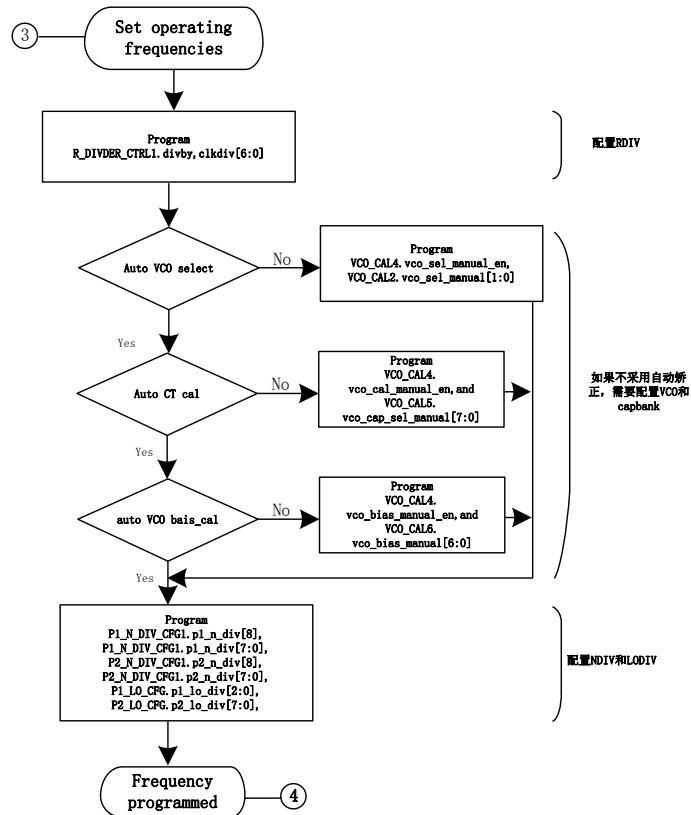

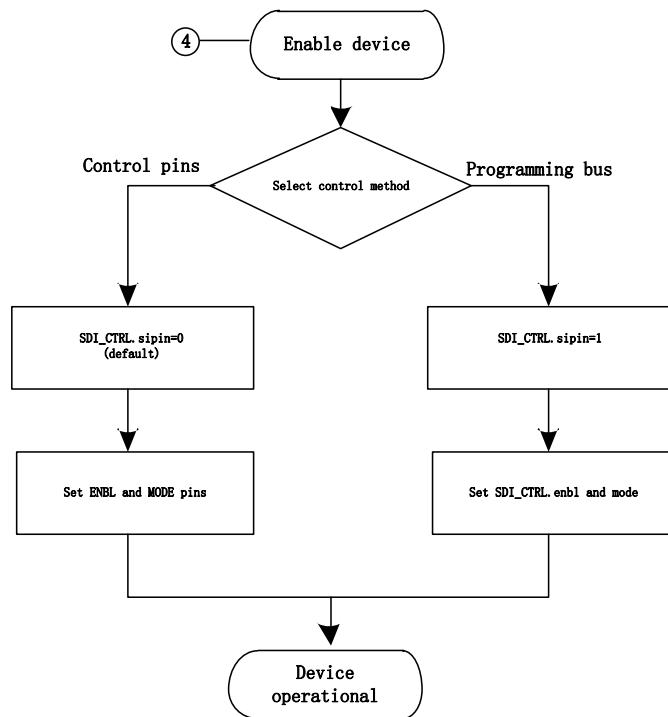

| 6 芯片配置流程                          | 47 |

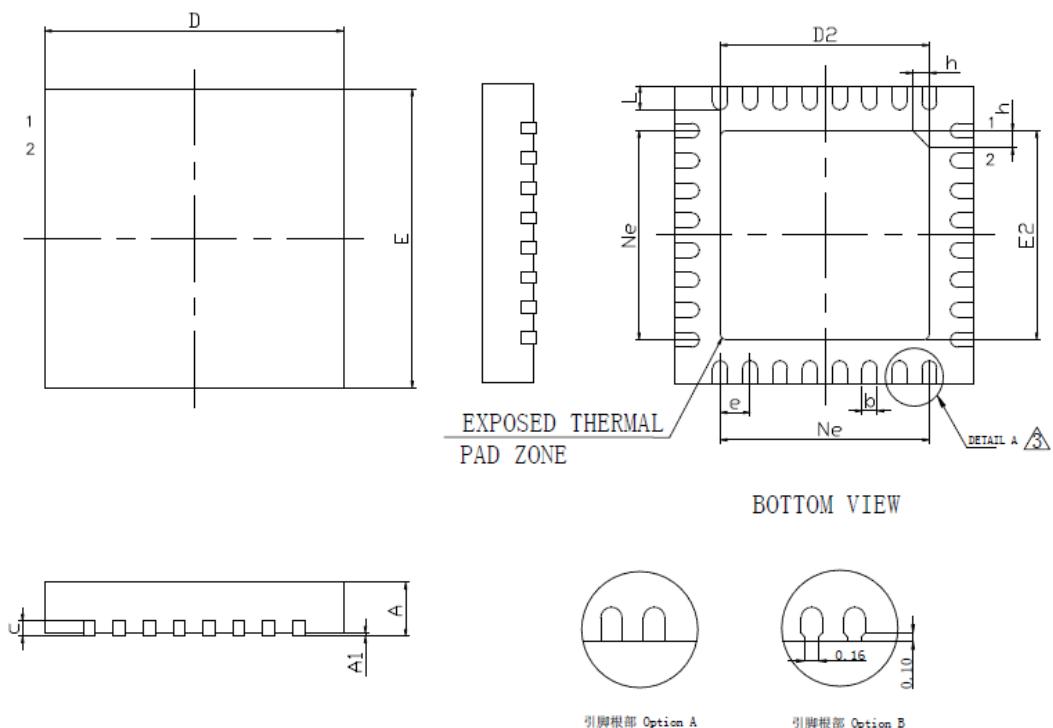

| 7 外形尺寸                            | 51 |

## 1. 引脚描述

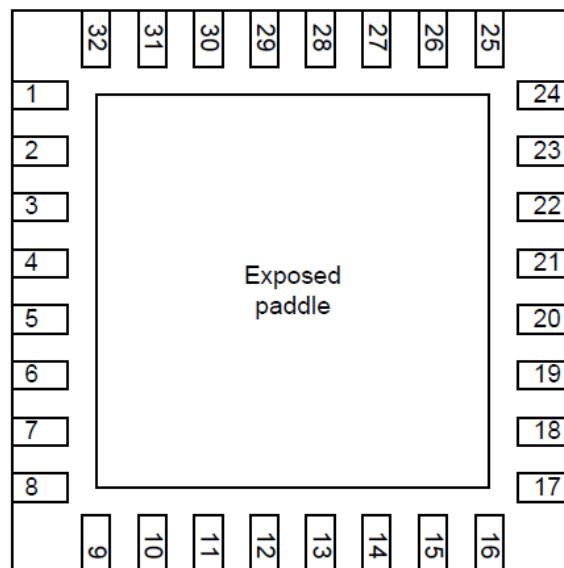

### 1.1 引脚布局图

图 2 引脚图(顶视图)

### 1.2 引脚功能说明

表 1 引脚功能定义

| 编号                              | 名称        | 功能说明             | 编号 | 名称              | 功能说明          |

|---------------------------------|-----------|------------------|----|-----------------|---------------|

| 1                               | ENBL/GP05 | 使能/通用脚           | 17 | MIX1_OPN        | Mixer 差分输出    |

| 2                               | EXT_LO    | 外部本振正端           | 18 | MIX1_OPP        | Mixer 差分输出    |

| 3                               | EXT_LO_N  | 外部本振负段           | 19 | DIG_VDD         | 数字电源, 需去耦滤波   |

| 4                               | REXT      | 外部偏置电阻 (10.8k Ω) | 20 | pin20_PLL_OUT_P | PLL 输出正端      |

| 5                               | ANA_VDD1  | 模拟电源脚, 需 RF 去耦滤波 | 21 | pin21_PLL_OUT_N | PLL 输出负段      |

| 6                               | LFILT1    | 封装内部键合到热沉地       | 22 | ANA_VDD2        | 模拟电源, RF 去耦滤波 |

| 7                               | LFILT2    | CP 输出脚           | 23 | MIX2_IPP        | Mixer 差分输入    |

| 8                               | LFILT3    | VCO 的控制电压输入脚     | 24 | MIX2_IPN        | Mixer 差分输入    |

| 9                               | MODE/GP06 | 模式选择脚            | 25 | GP03            | 通用输出脚         |

| 10                              | REF_IN    | 参考输入正端, AC 耦合输入  | 26 | GP04/LD/DO      | 通用输出脚         |

| 11                              | REF_IN_N  | 参考输入负段, AC 耦合输入  | 27 | MIX2_OPN        | Mixer 差分输出    |

| 12                              | TM        | 测试脚 (默认输出为高阻)    | 28 | MIX2_OPP        | Mixer 差分输出    |

| 13                              | MIX1_IPN  | Mixer 差分输入       | 29 | RESETX          | 芯片复位, 低有效     |

| 14                              | MIX1_IPP  | Mixer 差分输入       | 30 | ENX             | 串口使能          |

| 15                              | GP01/ADD1 | 通用输出脚            | 31 | SCLK            | 串口时钟          |

| 16                              | GP02/ADD2 | 通用输出脚            | 32 | SDATA           | 串口数据          |

| Exposed paddle: 通过低阻走线接到 PCB 的地 |           |                  |    |                 |               |

## 2 参数规格

### 2.1 绝对最大额定值

表 2 绝对最大额定值

| 电气参数                          | 额定值                |

|-------------------------------|--------------------|

| ANA_VDD1                      | -0.5V~3.6V         |

| ANA_VDD2                      | -0.5V~3.6V         |

| DIG_VDD                       | -0.5V~3.6V         |

| Input Voltage V <sub>IN</sub> | -0.3V~DIG_VDD+0.3V |

| RF/IF mixer input power       | +15dBm             |

| VESD                          | 1500V (HBM)        |

| 工作温度范围                        | -40°C~+85°C        |

| 存储温度范围                        | -65°C~+150°C       |

### 2.2 参数

除非另有说明, ANA\_VDD1=ANA\_VDD2=DIG\_VDD=3V, T<sub>A</sub>=25°C。

表 3 参数特性表

| 参数                    | 符号                    | 条件                         | 最小    | 典型   | 最大   | 单位  |  |

|-----------------------|-----------------------|----------------------------|-------|------|------|-----|--|

| 输入低电压                 | V <sub>IL</sub>       | 逻辑输入、输出脚                   | -0.3  |      | 0.5  | V   |  |

| 输入高电压                 | V <sub>IH</sub>       |                            | 2.2   |      | 3.3  | V   |  |

| 输入低电流                 | I <sub>IL</sub>       |                            | -10   |      | 10   | μA  |  |

| 输出高电流                 | I <sub>IH</sub>       |                            | -10   |      | 10   | μA  |  |

| 输出低电压                 | V <sub>OL</sub>       |                            | 0     |      | 0.66 | V   |  |

| 输出高电压                 | V <sub>OH</sub>       |                            | 2.64  |      | 3.3  | V   |  |

| Sink 电流               | I <sub>sink</sub>     | GPO 口驱动能力                  | 10    | 20   |      | mA  |  |

| Source 电流             | I <sub>source</sub>   |                            | 10    | 20   |      | mA  |  |

| 输出电阻                  | R <sub>out</sub>      |                            |       |      | 30   | Ω   |  |

| 待机电流                  | I <sub>standby</sub>  |                            |       |      | 5    | mA  |  |

| 关断电流                  | I <sub>poweroff</sub> |                            |       |      | 3    | mA  |  |

| 电源电流<br>(一个 mixer 工作) | I <sub>DD</sub>       | MIX_IDD=1                  |       | 78   |      | mA  |  |

|                       |                       | MIX_IDD=6                  |       | 99   |      | mA  |  |

| 增益                    | gain                  | Mixer<br>输出驱动<br>4:1 balun | -9.5  | -2   |      | dB  |  |

| 噪声系数                  | noisefigure           |                            |       | 10   | 18   | dB  |  |

|                       |                       |                            |       | 13   | 24   | dB  |  |

|                       |                       |                            | 低电流模式 | 0    | +12  | dBm |  |

| 三阶交调                  | IIP3                  |                            | 高电流模式 | 13.5 | +23  | dBm |  |

| 输入频率范围                | f <sub>in</sub>       |                            |       | 30   |      | MHz |  |

| 输入损耗                  | inputloss             |                            |       |      | 23   | dB  |  |

| 输出频率范围                | f <sub>out</sub>      |                            |       | 30   |      | MHz |  |

| 参考输入频率范围              | f <sub>ref</sub>      | 参考输入脚                      | 10    |      | 104  | MHz |  |

## BS6302 3GHz 频率转换器

| 参数                  | 符号               | 条件             | 最小      | 典型   | 最大   | 单位  |

|---------------------|------------------|----------------|---------|------|------|-----|

| 参考输入幅度              | Levelref         |                | 500     | 800  | 1500 | mV  |

| 频率合成器输出频率范围         | $f_{\text{p11}}$ |                | 90      |      | 3700 | MHz |

| 鉴相频率                | $f_{\text{pf1}}$ |                |         |      | 52   | MHz |

| 相位噪声 (LO=1GHz)      | Phase noise      | 参考频率：<br>50MHz | @10kHz  |      | -108 |     |

|                     |                  |                | @100kHz |      | -108 |     |

|                     |                  |                | @1MHz   |      | -135 |     |

|                     |                  |                | @10kHz  |      | -102 |     |

|                     |                  |                | @100kHz |      | -102 |     |

|                     |                  |                | @1MHz   |      | -130 |     |

| VCO 在频偏<br>1MHz 在相噪 | Phase noise      | @2.5 GHz       |         | -134 |      |     |

|                     |                  | @2 GHz         |         | -135 |      |     |

|                     |                  | @1.5 GHz       |         | -136 |      |     |

| 外部本振输入频率范围          | $f_{\text{lo}}$  |                | 90      |      | 4000 | MHz |

| 外部本振频信号幅度           | LevelLo          |                |         | 0    |      | dBm |

### 3 工作原理

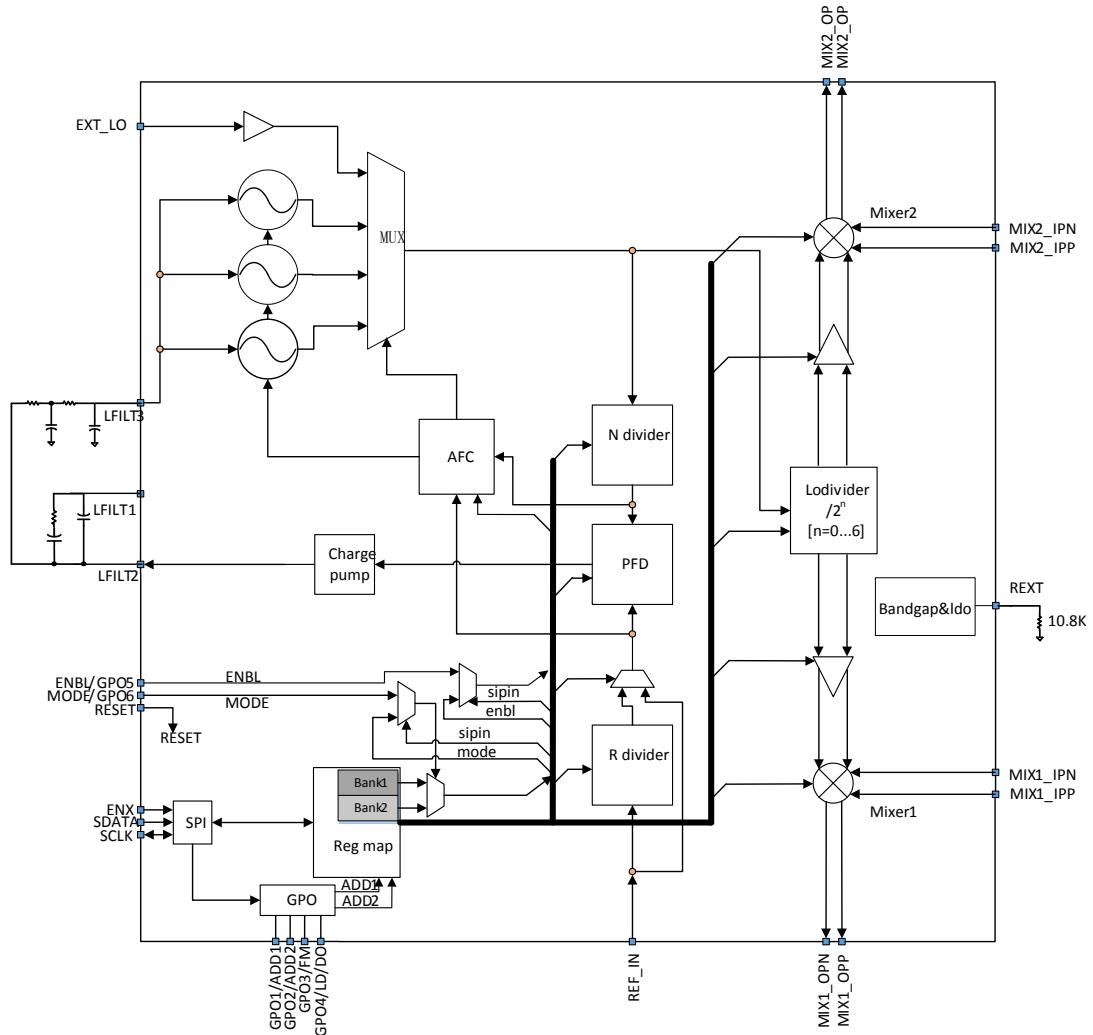

#### 3.1 功能框图

BS6302 芯片是一款宽带宽 RF 频率转换器，内置有整数频率合成器、RF 混频器、基准源和 LDO 等。芯片可通过 3 线串口进行配置内部的寄存器，具体功能框图如下所示。

图 3 功能框图

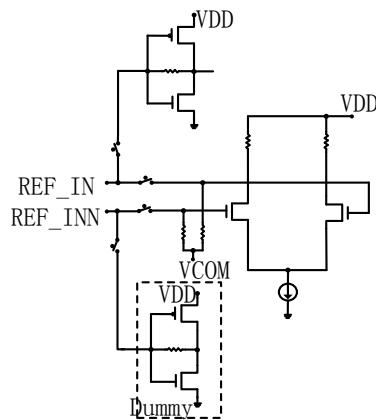

### 3.2 参考输入

芯片的参考输入支持单端模式和差分模式，输入片频率范围 10MHz~400MHz，如下图。

图 4 参考输入电路

单端输入电路是自偏置的，差分输入内部提供共模点。可以通过寄存器 PLL\_CTRL1[1]选择差分或单端输入。单端信号从 REF\_IN 脚输入，可以用 DC 耦合的 CMOS 信号驱动或 AC 耦合的正弦波驱动；差分信号从 REF\_IN/REF\_IN\_N 脚输入，可以用 AC 耦合的 LVDS 信号或 LVPECL 信号驱动。

### 3.3 鉴频鉴相器 PFD 和电荷泵 chargepump 电路

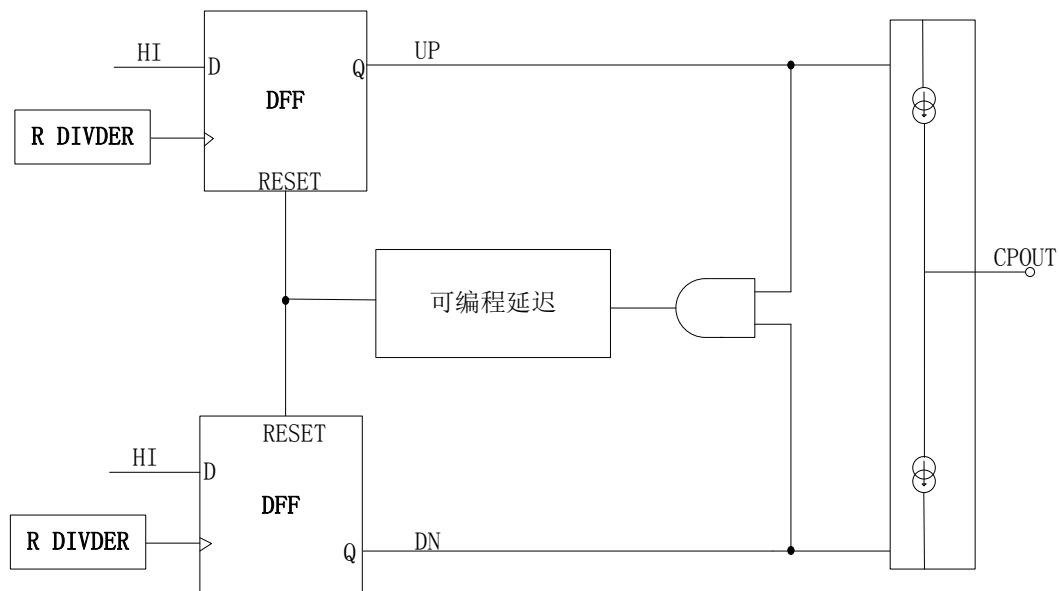

鉴频鉴相器 PFD 由两个 D 触发器和延时单元构成，监测参考分频器 Rdivder 和反馈分频器 Ndivder 的相位差和频率差，产生等比例的脉冲信号去驱动电荷泵对环路滤波器进行充电或放电，从而产生 VCO 的调谐电压。CP 的电流可配置， $I_{CP}=600\mu A \times (PFD\_CUR\_CTRL[7:5]+1)$ 。

图 5 PFD+chargepump 电路

电荷泵 chargepump 工作模式可配置为高阻模式，正常工作模式，和测试模式。

- PFD\_CUR\_CTRL[3:2]=00, CP 为正常工作模式；

- PFD\_CUR\_CTRL[3:2]=01, CP 为测试模式，UP=0, DN=0, UP 电流开启，测试 UP 电流；

- PFD\_CUR\_CTRL[3:2]=10, CP 为测试模式，UP=1, DN=1, DN 电流开启，测试 DN 电流；

- PFD\_CUR\_CTRL[3:2]=11, CP 为高阻模式，UP=1, DN=0, UP 和 DN 电流都关断；

### 3.4 分频器

芯片中有三个分频器，参考分频器 Ref divider，反馈分频器 N divider，本振分频器 Lo divider。

- Rdivider 对参考频率进行分频，分频范围为 1~127。寄存器 R\_DIVDER\_CTRL1 可配置分频比。当 R\_DIVDER\_CTRL1[7]=1 时，R divider 分频比为 1；R\_DIVDER\_CTRL1[7]=0 时，R divider 分频比 2~127 通过 R\_DIVDER\_CTRL1[6:0] 进行配置。

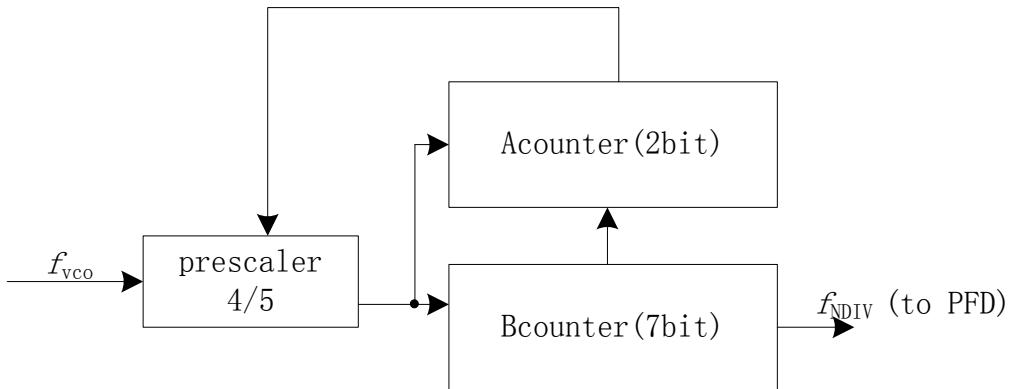

- b) N divider 对 VCO 的输出进行分频, 由 prescaler, A/B counter 组成如下图, 分频范围 20~511。PLLbank1 NDIV 由寄存器 P1\_N\_DIV\_CFG1[0] & P1\_N\_DIV\_CFG2[7:0] 配置; PLLbank2 NDIV 由寄存器 P2\_N\_DIV\_CFG1[0] & P2\_N\_DIV\_CFG2[7:0] 配置。

图 6 N DIV 功能图

- c) Lo divider 对频率合成器输出进行分频, 分频范围为  $2^n$  ( $n=0, 1, 2, 3, 4, 5, 6$ )。PLLbank1 由寄存器 P1\_LO\_CFG[2:0] 配置; PLLbank2 由寄存器 P2\_LO\_CFG[2:0] 配置;

### 3.5 压控振荡器 LC VCO

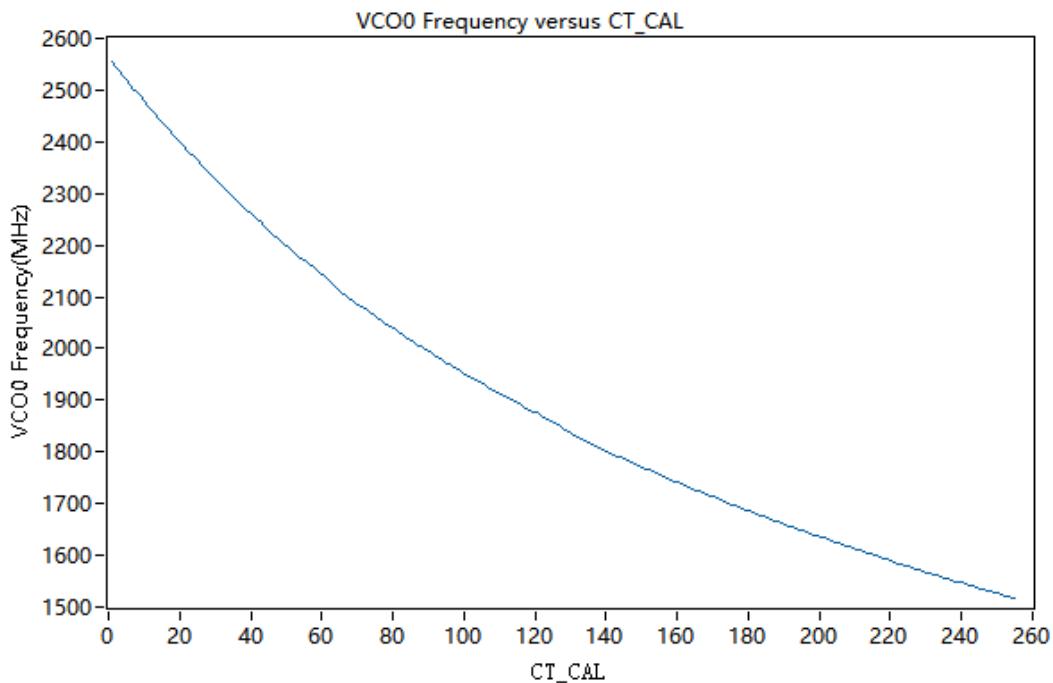

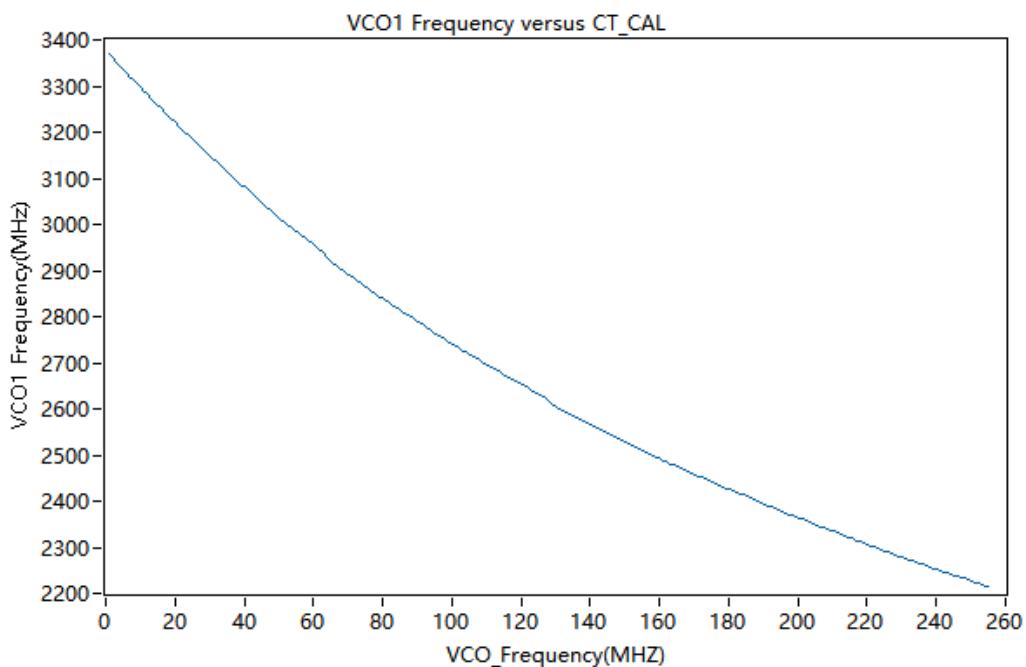

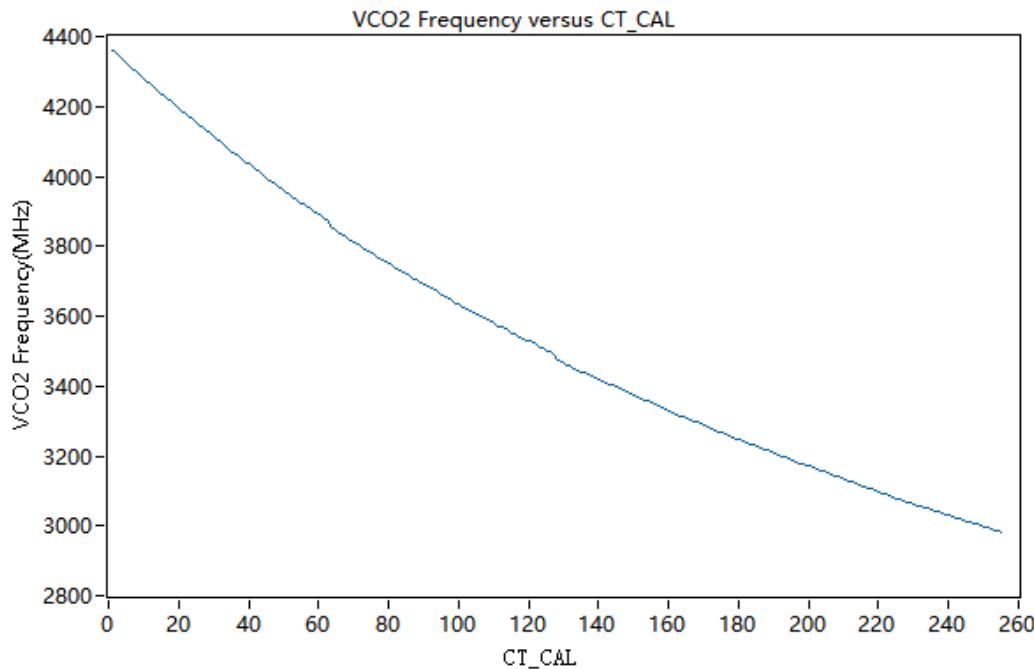

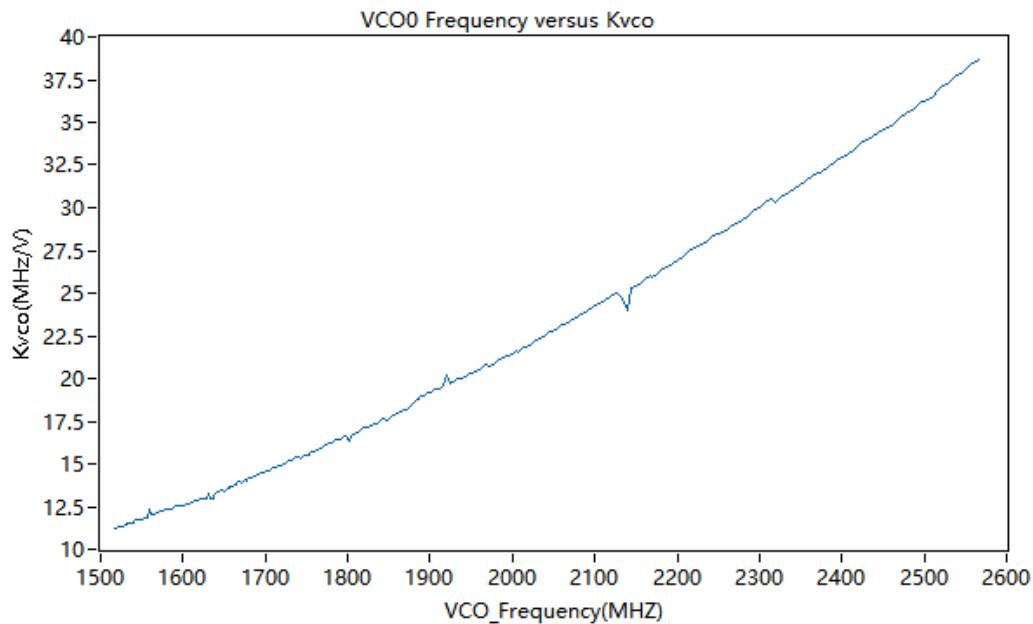

芯片中的 VCO 内核由三个 LCVCO 组成, VCO 频率覆盖范围 2GHz~4GHz 在。VCO 和 LO divider 结合使用时, 本振的频率范围 30MHz~4GHz。每个 VCO 有 255 个频段, 用于在整个调谐范围内实现低 VCO 增益和低相噪声性能。VCO 内部有自动校准算法, 根据输入的配置能自动选择 VCO 和 VCO 频段。配置芯片引脚 ENBL 或寄存器 0x005[2] relock 为高时, 会触发校准。校准完成后, 选择了正确的 VCO 和频段, 频率合成器将锁定到正确的频率。在频段选择过程中, 连接到 VCO 谐振回路的电容阵列逐步增加, 直到 VCO 的频率和设置一致。选择的频段值 CT\_CAL 在回读寄存器中可用。此寄存器中的值 255 或 0 表示粗调不成功, 这也将由回读寄存器中的 CT\_FAILED 标志指示。介于 1 和 254 之间的 CT\_CAL 值表示校准成功。VCO 自动校正算法能使锁定的调谐电压在 1.5V 附近, 同时 VCO 内部的有频率补偿的温度, 可以补偿工艺和温度等偏差引入的 VCO 频率变化。芯片要幅度检测功能, 可以自动调节 VCO 电流, 使 VCO 工作在最佳状态。

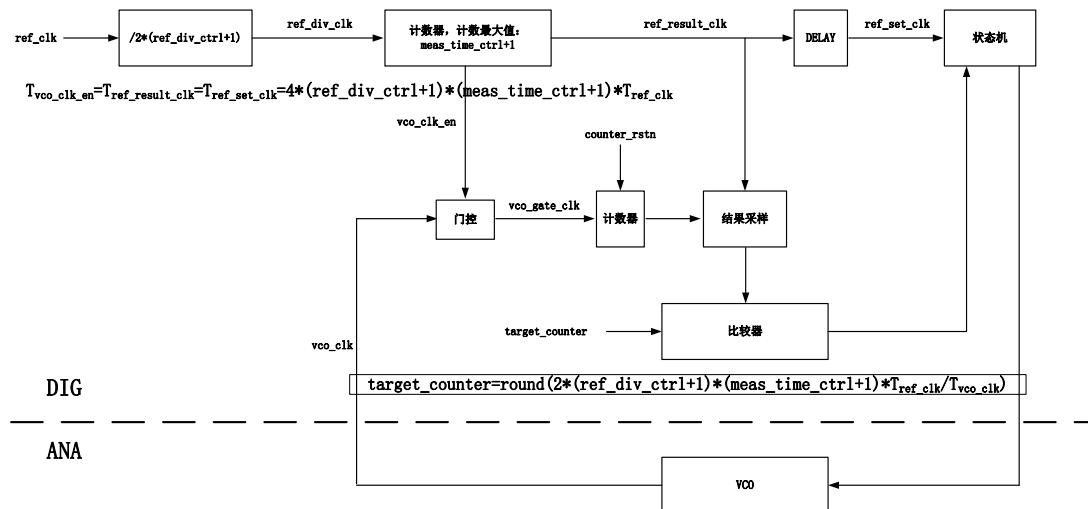

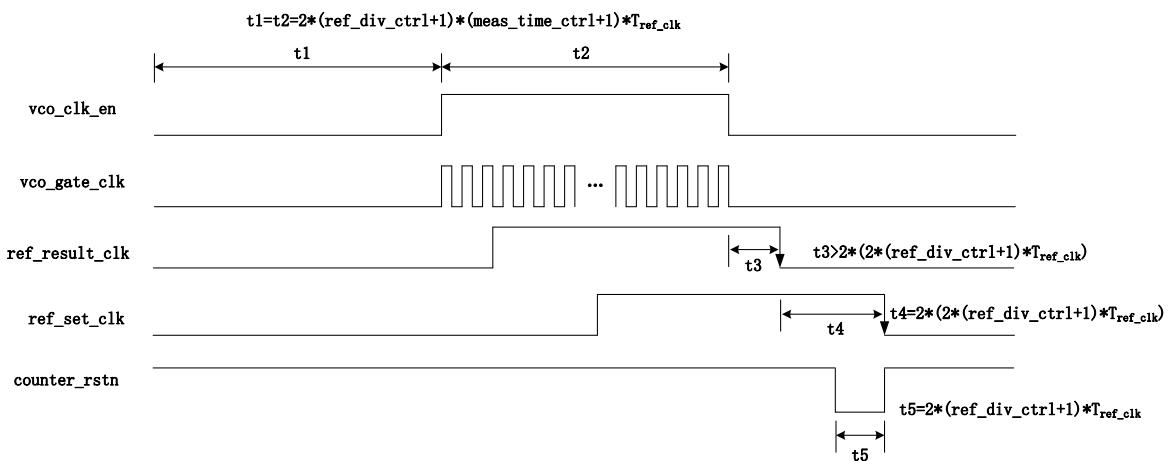

开环校正功能实现的逻辑框图及信号时序如下。ref\_clk 的分频时钟用于计数并产生 vco\_clk\_en 信号, 该信号高电平用于使能 vco\_clk 计数, 低电平时间段用于等待 PLL 输出稳定。ref\_result\_clk、ref\_set\_clk 与 vco\_clk\_en 同频率, 并有固定的相位关系, 分别用于计数结果的锁存和状态机逻辑。计数器结果锁存后, counter\_rstn 信号将对计数器进行异步复位, 为下一次计数做好准备。

图 7 校正逻辑框图

图 8 校正逻辑时序图

### 3.6 锁定检测电路

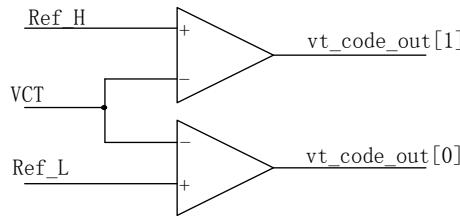

频率合成器有数字和模拟锁定检测电路。数字锁定检测电路检测输入给鉴频鉴相器的参考分频时钟和环路反馈分频时钟的相位误差来判断环路是否锁定。相位误差的阈值可由寄存器 **PLL\_CTRL1[3]** / **LDT\_CTRL[7:4]** 配置，同时输出的数字锁定指示信号能通过引脚 pin26 或寄存器 **VCO cal26[0]** 进行回读。模拟锁定检测电路由两个比较器组成，如下图。通过检测调谐电压的范围来判断锁定情况。Ref\_H (default: 1.728V) 和 Ref\_L (default: 1.279V) 为比较窗口电压。比较结果 **vt\_code\_out[1:0]** 存在寄存器 **VCOcal[3:2]** 中，可以回读。当 **vt\_code\_out[1:0]=00**，时表示锁定；当 **vt\_code\_out[1:0]=01** 表示失锁， $VCT < Ref\_L$ ；**vt\_code\_out[1:0]=10** 表示失锁， $VCT > Ref\_H$ ；另外锁定窗口的高低比较电压可以通过寄存器 **COMP\_CTRL[6:4]** / **COMP\_CTRL[3:1]** 进行设置。

图 9 模拟锁定检测电路

### 3.7 宽频带混频器 mixer

芯片中有两个可以独立工作的 mixer，工作频率范围为 30MHz~3700MHz，可实现上变频和下变频。mixer 采用双平衡的 Gilbert 单元电路实现。开漏输出，外接中心抽头的巴伦。电流从电源经 balun 流入 mixer。mixer 的工作电流通过寄存器 MIX\_CTRL2<6:4>进行配置，配置范围 7mA~54mA，以实现 mixer 不同线性度的要求。

Mixer 的输入和输出端均为全差分电路，对某些特定的频点，需用简单匹配电路优化性能。当差分输入阻抗为  $100\Omega$ ，差分负载阻抗为  $200\Omega$  时，mixer 的转换增益为-2dB，另外增加负载阻抗可以增加转换增益。

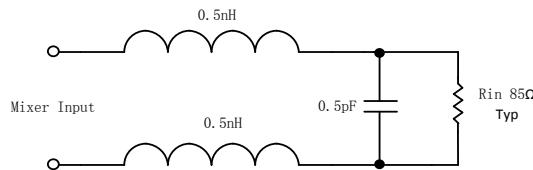

Mixer 采用共栅输入结构，输入阻抗和输入管的跨导成反比，因此和 mixer 的工作电流成反比。在默认配置下，输入电阻约为  $85\Omega$ 。另外在高频下，阻抗需要考虑输入端的并联电容和 bond 线电感（约  $0.5nH$ ），下图是 mixer 输入阻抗的简化模型。

图 10 mixer 输入阻抗简化模型

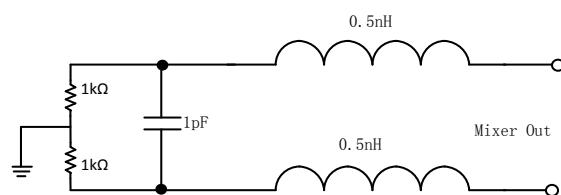

Mixer 的输出为高阻的开漏输出，输出阻抗可由约  $2k\Omega$  电阻和约  $1pF$  电容并联进行等效。输出不需要共轭匹配匹配网络。mixer 的输出为恒流源，可以驱动  $50\Omega$  到  $500\Omega$  的差分负载，典型值采用  $200\Omega$ 。增大负载电阻可以增加输出信号幅度和增益。在高频时，输出阻抗需要考虑 bond 线（约  $0.5nH$ ），下面是 mixer 输出阻抗的简化模型。

图 11 mixer 输出阻抗简化模型

Mixer 可以设置为在半双工模式（1 个混频器使能）或全双工模式（两个混频器都使能）下运行。该选择是通过控制 MODE 和设置 FULLD 位来完成的。在全双工模式下，可以使用任一 PLL 寄存器组，本振信号同时输入到两个混频器。

| Mode | FULLD | Active PLL Register Bank | Active Mixer |

|------|-------|--------------------------|--------------|

| Low  | 0     | 1                        | 1            |

| High | 0     | 2                        | 2            |

| Low  | 1     | 1                        | 1 and 2      |

| High | 1     | 2                        | 1 and 2      |

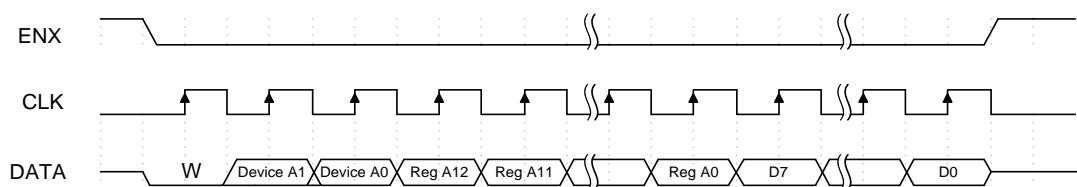

### 3.8 串行接口

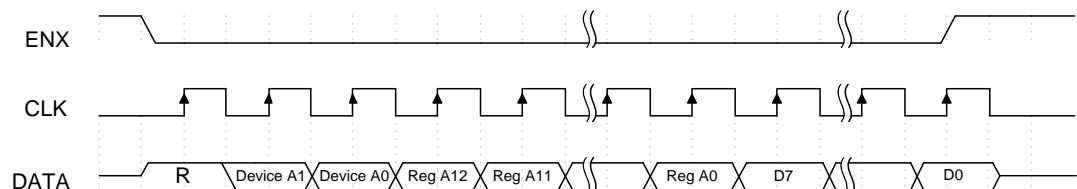

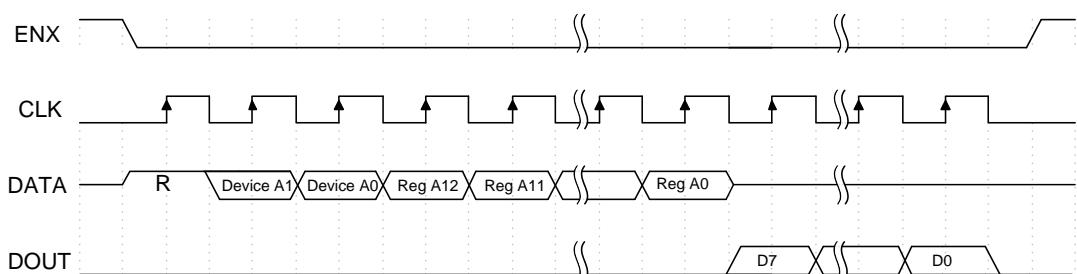

BS6302 中的所有片上寄存器均使用支持写入和读取操作的专有 3 线串行总线进行编程。合成器编程、设备配置和控制是通过硬件和软件控制的混合实现的。除了通过串行总线进行编程之外，某些功能和操作还需要通过 ENBL、MODE 和 RESETX 引脚使用硬件控制。或者，可以选择通过串行总线完全控制芯片通过将寄存器 4wire 位设置为高电平，可以将串行数据接口配置为 4 线操作。然后 26 引脚 DO 为数据输出脚，32 引脚 SDATA 为串口数据输入脚。

图 12 三线写时序

图 13 三线读时序

图 14 四线读时序

### 3.9 硬件控制

提供了三个硬件控制引脚：ENBL、MODE 和 RESETX。

a) ENBL 引脚有两个功能：启用芯片中的模拟电路和触发 VCO 自动选择和粗调机制。

当 ENBL 引脚为高电平时，将启动 VCO 自动选择和粗调。每次重新编程合成器的频率时，必须将 ENBL 置为高电平以启动这些机制，然后启动 PLL 锁定。或者，在新频率编程之后，可以使用 PLL 重新锁定自清除位。

- b) RESETX 引脚是一个硬件复位控制，当断言为低电平时，它将所有数字电路复位到它们的启动状态。该器件具有上电复位功能，因此通常不需要此引脚，在这种情况下应将其连接到正电源。

- c) MODE 引脚控制哪个混频器和 PLL 编程寄存器组处于活动状态。

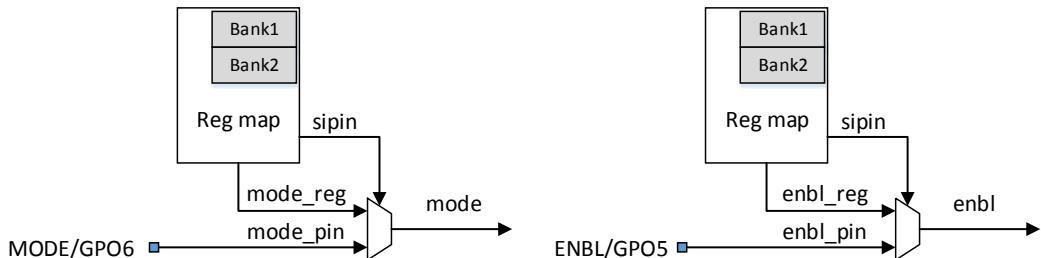

当寄存器 `sipin` 为 1 时 ENBL 和 MODE 引脚被忽略并作为 GPO5 和 GPO6，由寄存器 `enlb` 和 `mode` 替代 ENBL 和 MODE 引脚功能。

图 15 enlb 和 mode 的选择逻辑框图

### 3.10 串行数据接口控制

正常操作模式使用 3 线串行数据接口对设备寄存器进行编程，并使用三个额外的硬件控制线：MODE、ENBL 和 RESETX。

当设备处于软件控制下时，通过将寄存器 `sipin` 设置为高来实现，则可以通过寄存器控 `enlb` 和 `mode` 制硬件。在这种情况下，不需要三个硬件控制线。如果器件受软件控制，则引脚 1 和 9 可配置为通用输出 (GPO)。

### 3.11 多片模式

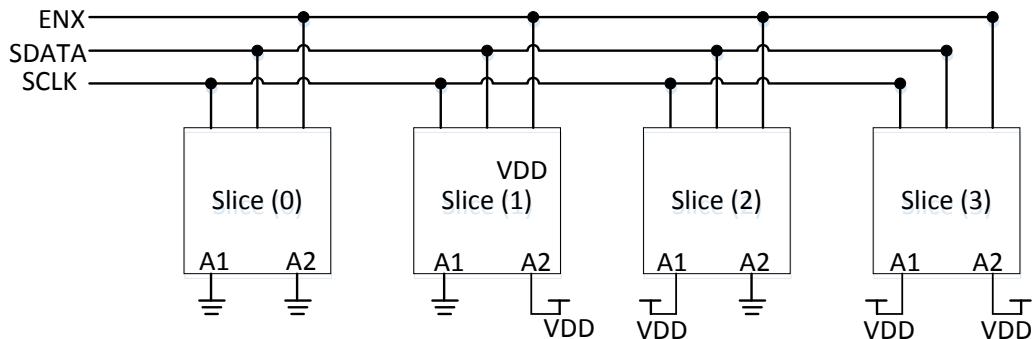

图 16 多片模式硬件连接图

多片操作模式允许从公共串行总线控制多达四个芯片。器件地址引脚 (15 和 16) ADD1 和 ADD2 用于设置每个部分的地址。

上电和复位后，器件会忽略地址引脚 ADD1 和 ADD2，并且提供给串行总线的任何数据都将被编程到所有器件中。但是，一旦设置了寄存器中的 `addr` 位，每个设备就会根据设备上地址引脚的状态采用一个地址，此时地址值为{ADDR1,ADDR0,REG\_ADDR[12]}。

### 3.12 通用接口 GPO

通用输出 (GPO) 可以通过 GPO 寄存器进行控制，并且取决于 MODE 的状态，因为它们可以设置为对应于混频器路径 1 或 2 的不同状态。此处需要使用 bank1、bank2。

GPO1\_ADD1 与 GPO2\_ADD2 可以作为设备地址 ADDR 输入和 GPO 输出，当寄存器 addr (寄存器 0x001 的 bit3) 为高时，使能为设备地址 ADDR 引脚；否则如果使能寄存器 gpo\_gate 则根据 mode 决定输出寄存器 p1gpo\_val[0]、p1gpo\_val[1] 或者 p2gpo\_val[0]、p2gpo\_val[1] 中的值；否则为高阻态。

GPO3 在寄存器 gpo\_gate 为高，则根据 mode 决定输出寄存器 p1gpo\_val[2] 或者 p2gpo\_val[2] 中的值；否则为高阻态。

GPO4\_LD\_DO 如果寄存器 4wire 为高，则器件被配置为四线总线，读取操作的数据输出被转到 GPO4\_LD\_DO 而不是 SDATA 引脚。如果寄存器 lock\_gate 和寄存器 4wire 都为高，则 enbl 为高时输出锁定指示，而当设 enbl 为低时作为四线 spi 读取输出；否则如果使能寄存器 gpo\_gate 则根据 mode 决定输出寄存器 p1gpo\_val[3] 或者 p2gpo\_val[3] 中的值；否则为高阻态。

GPO5\_ENBL 如果 sipin 为低时，作为 enbl 输入，否则如果使能寄存器 gpo\_gate 则根据 mode 决定输出寄存器 p1gpo\_val[4] 或者 p2gpo\_val[4] 中的值；否则为高阻态。

GPO6\_MODE 如果 sipin 为低时，作为 mode 输入，否则如果使能寄存器 gpo\_gate 则根据 mode 决定输出寄存器 p1gpo\_val[5] 或者 p2gpo\_val[5] 中的值；否则为高阻态。

## 4 参数测试波形

下面的性能测试波形是在电源  $V_{DD}=3.0V$ ，温度  $T_A=27^{\circ}C$  的条件下的测试结果。

### 4.1 电源电流测试

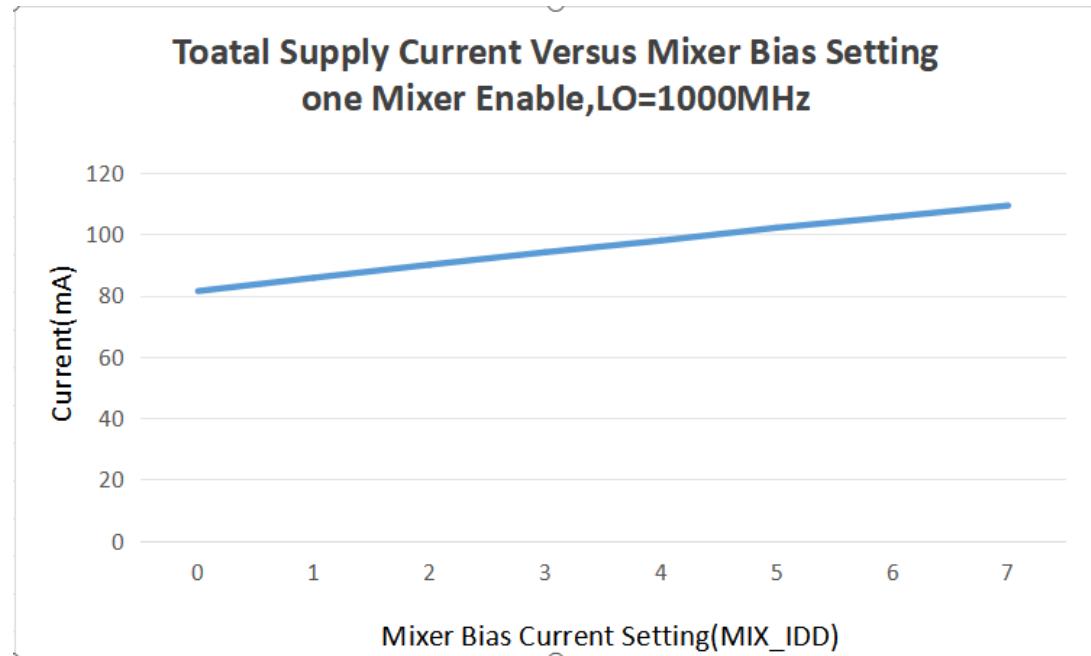

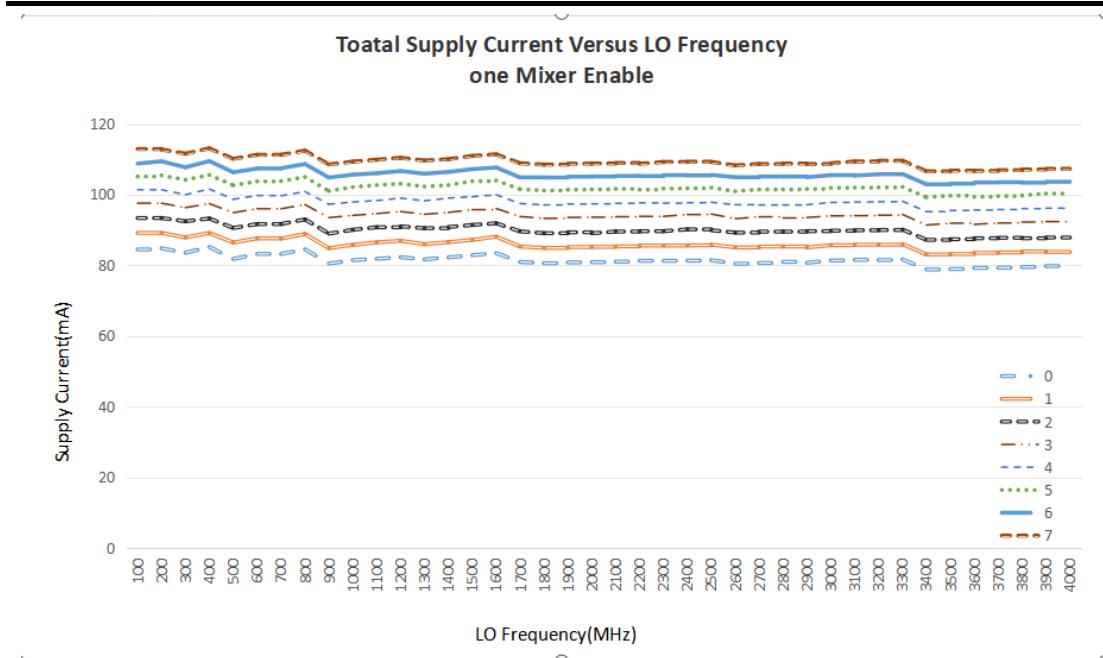

图 17 MIX2\_IDD=1~7, one mixer 工作时的电源电流

图 18 LO 频率 100MHz~4GHz, one mixer 工作时的电源电流

表 4 全双工模式下的电源电流

| MIX2_IDD | MIX1_IDD |         |         |         |         |         |         |         | 单位<br>mA |

|----------|----------|---------|---------|---------|---------|---------|---------|---------|----------|

|          | 0        | 1       | 2       | 3       | 4       | 5       | 6       | 7       |          |

| 0        | 74.085   | 78.544  | 82.674  | 87.002  | 91.002  | 95.199  | 99.002  | 103.002 |          |

| 1        | 78.412   | 82.871  | 87.068  | 91.396  | 95.199  | 99.527  | 103.396 | 107.786 |          |

| 2        | 82.478   | 86.937  | 91.458  | 95.527  | 99.264  | 103.658 | 107.461 | 111.852 |          |

| 3        | 86.872   | 91.199  | 95.721  | 99.658  | 103.592 | 107.789 | 111.723 | 115.723 |          |

| 4        | 90.609   | 95.134  | 99.133  | 103.461 | 107.461 | 111.592 | 115.917 | 119.983 |          |

| 5        | 94.806   | 99.264  | 103.589 | 107.789 | 111.592 | 115.855 | 119.789 | 123.854 |          |

| 6        | 98.609   | 103.199 | 107.133 | 111.592 | 115.395 | 119.658 | 123.592 | 128.048 |          |

| 7        | 102.674  | 107.199 | 111.33  | 115.723 | 119.786 | 123.722 | 127.658 | 131.854 |          |

## 4.2 频率合成器的相位噪声测试

### 4.2.1 鉴相频率为 50MHz 时的测试

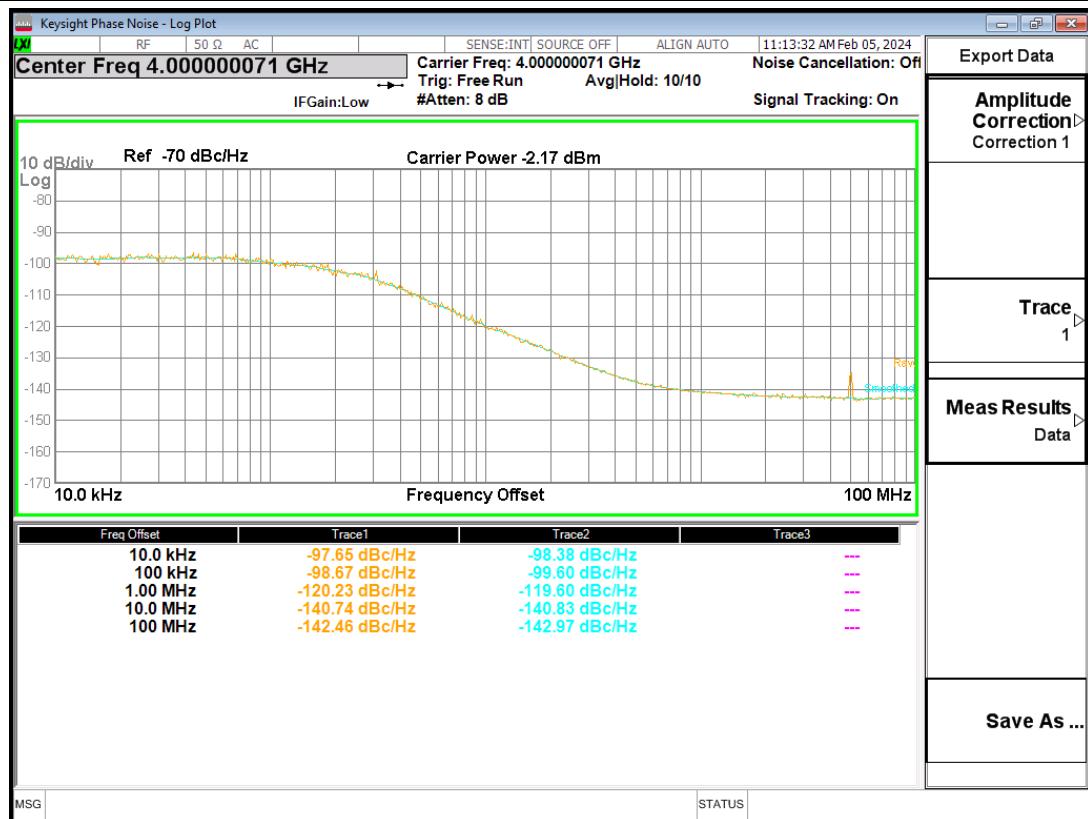

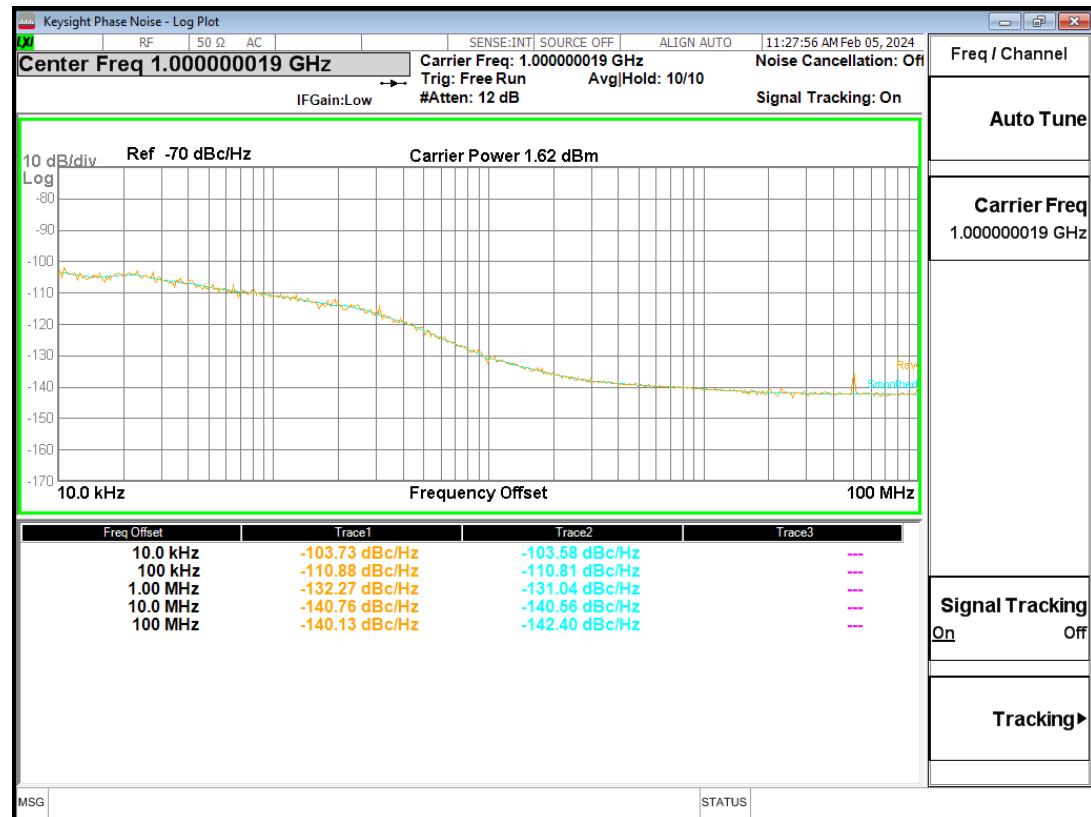

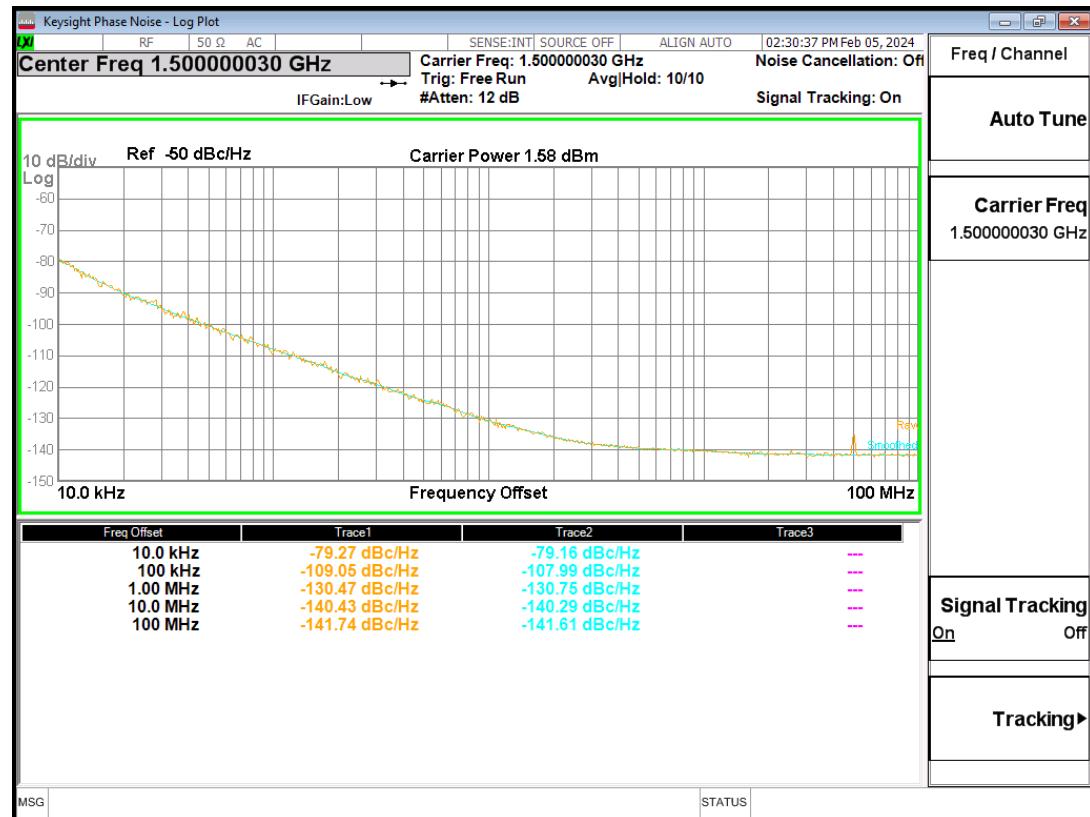

图 19  $fre=50\text{MHz}$ ,  $f_{vco}=4\text{GHz}$  时 PLL 相位噪声

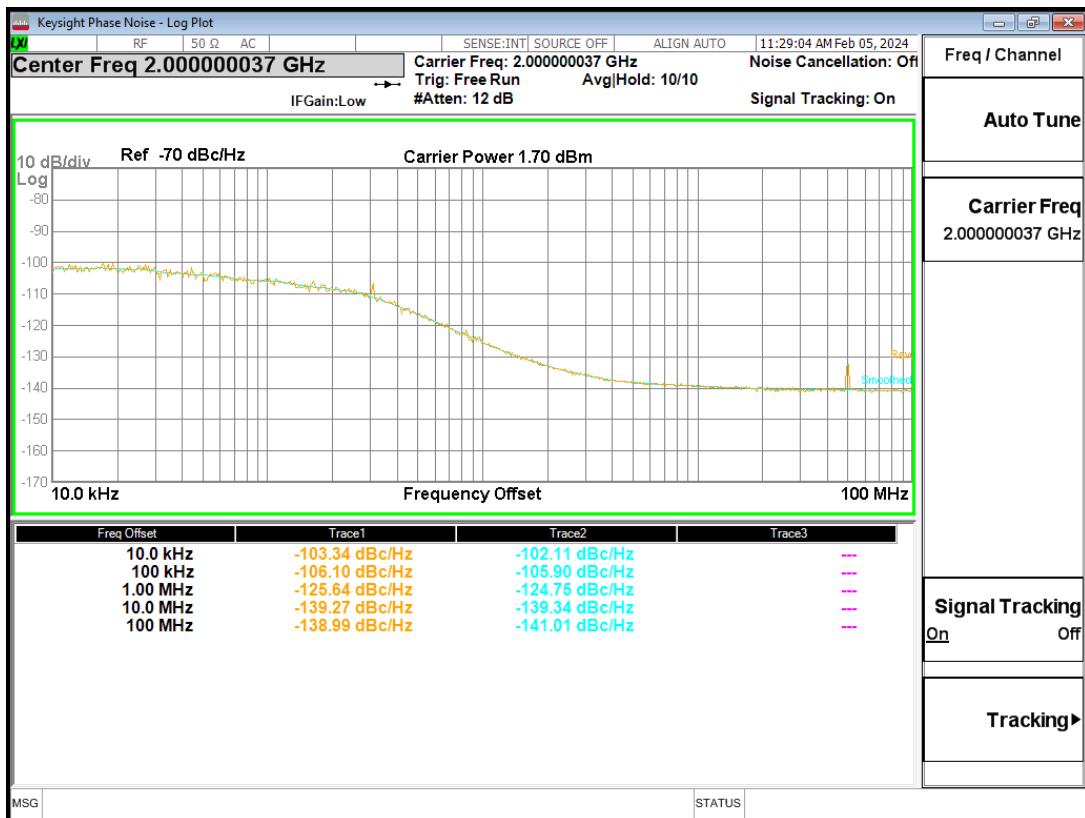

图 20 fre=50MHz, fvco=4GHz, Loddv 二分频时 PLL 相位噪声

图 21 fre=50MHz, fvco=4GHz, L0div 四分频时 PLL 相位噪声

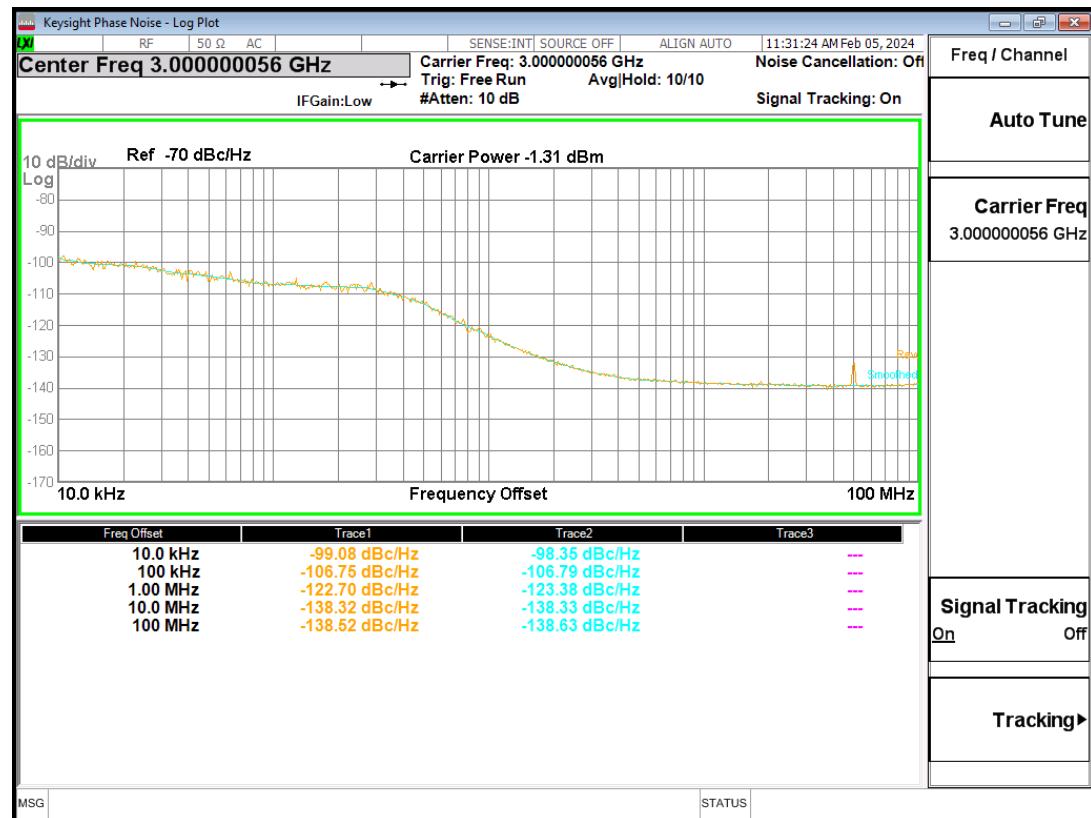

图 22 fre=50MHz, fvco=3GHz 时 PLL 相位噪声

图 23 fre=50MHz, fvco=3GHz, lodiv 二分频时 PLL 相位噪声

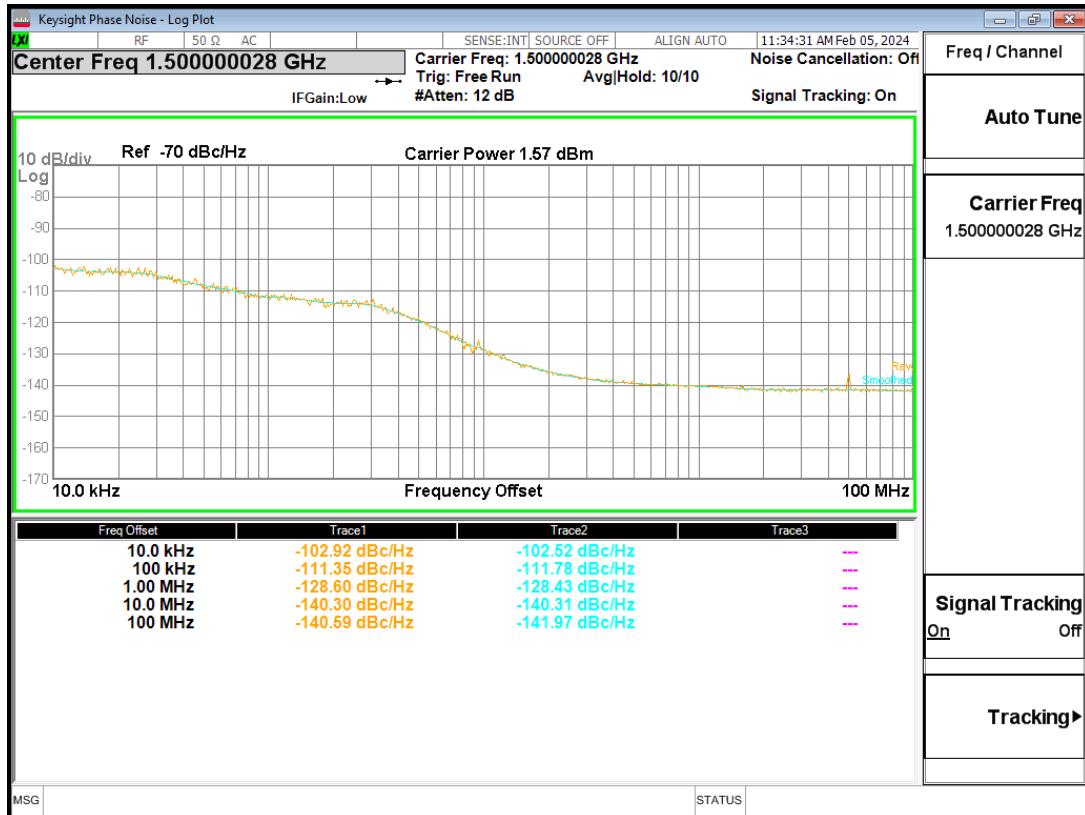

#### 4.2.2 鉴相频率为 25MHz 时的测试

图 24 fre=25MHz, fvco=4GHz 时 PLL 相位噪声

图 25 fre=25MHz, fvco=4GHz , Lodiv 二分频时 PLL 相位噪声

图 26 fre=25MHz, fvco=4GHz , Lodiv 四分频时 PLL 相位噪声

图 27  $\text{fre}=25\text{MHz}$ ,  $\text{fvco}=3\text{GHz}$  时 PLL 相位噪声

图 28 fre=25MHz, fvco=3GHz, lodiv 二分频时 PLL 相位噪声

#### 4.3 VCO 的性能测试

##### 4.3.1 VCO 的频率范围测试

图 29 VCO0 频率范围

图 30 VCO1 频率范围

图 31 VCO2 频率范围

#### 4.3.2 VCO 的 KV 测试测试

图 32 VCO0 全频率范围的 KVCO

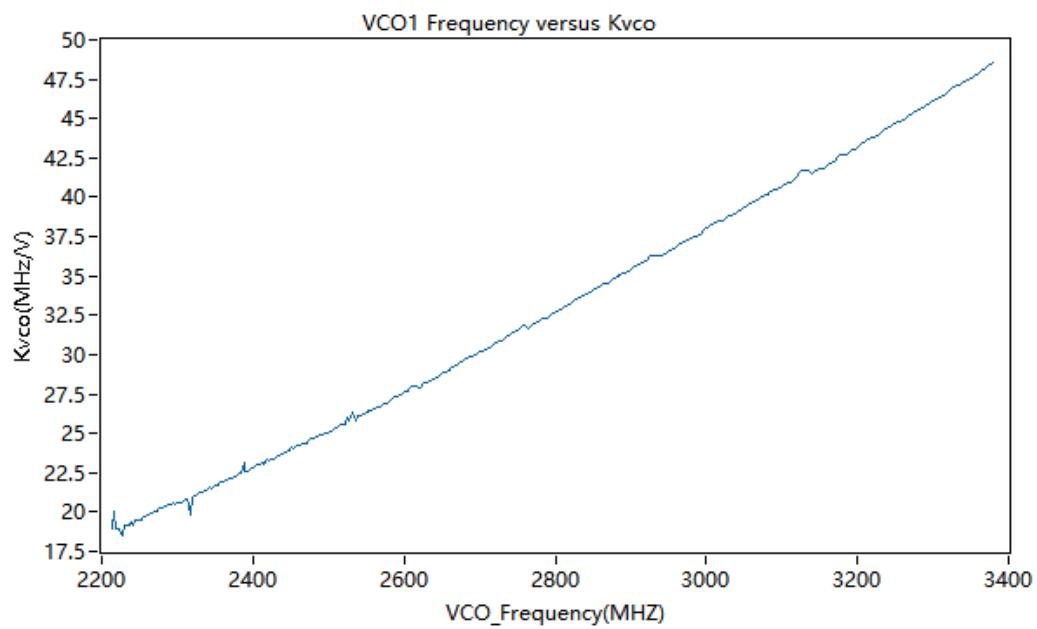

图 33 VCO1 全频率范围的 Kvco

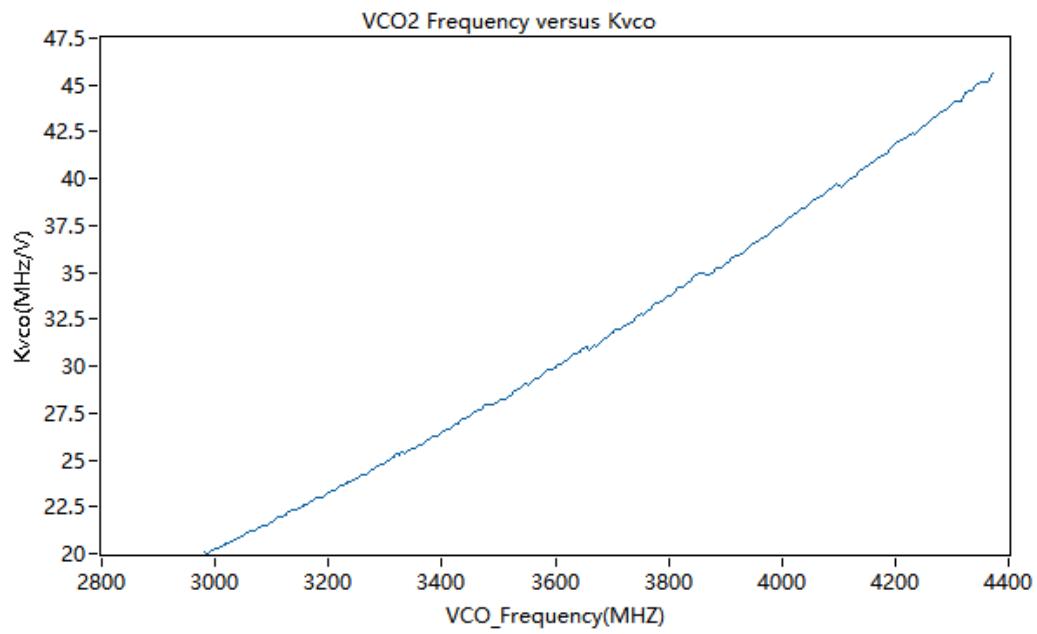

图 34 VCO2 全频率范围的 Kvco

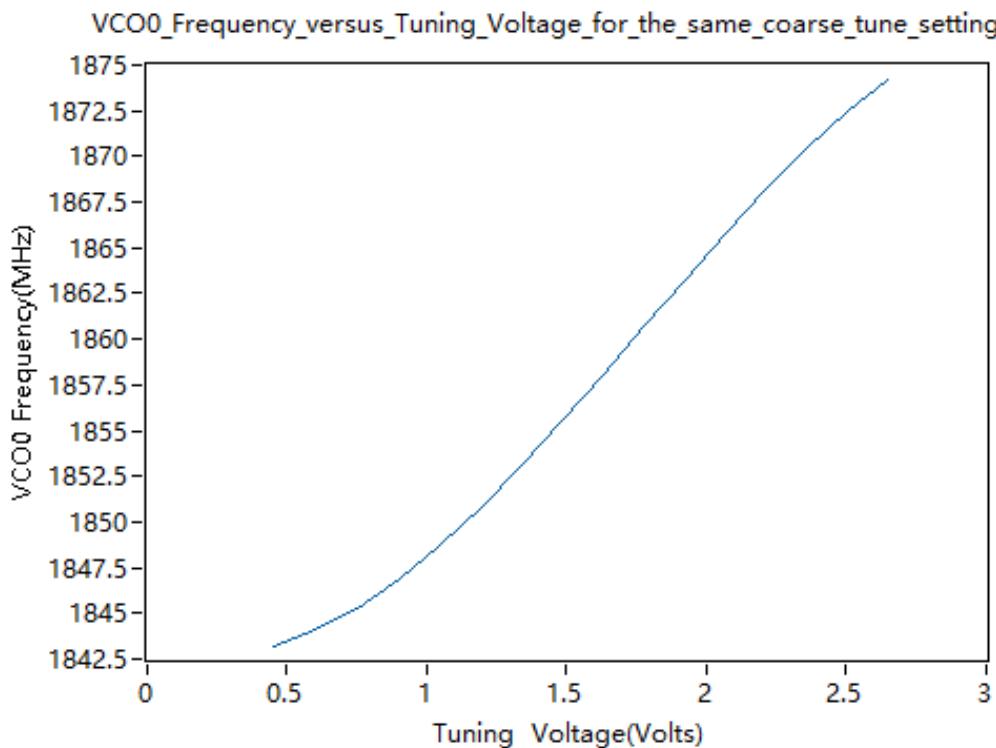

图 35 VCO0 CT\_CAL=127 时, 频率和调谐电压的关系

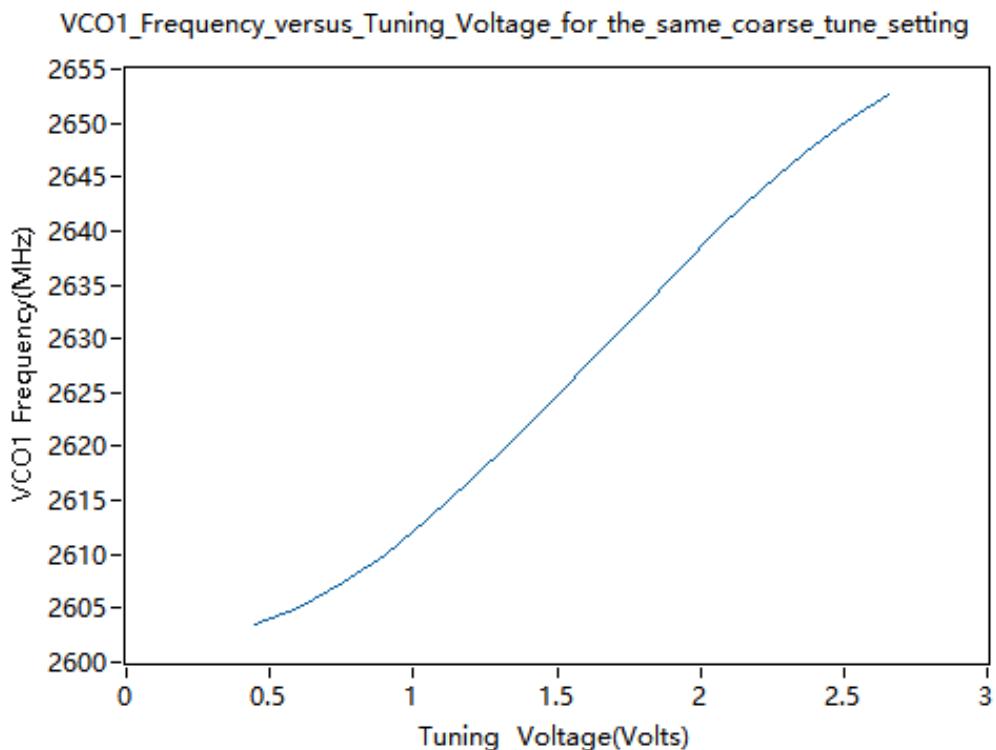

图 36 VCO1 CT\_CAL=127 时, 频率随调谐电压的变化

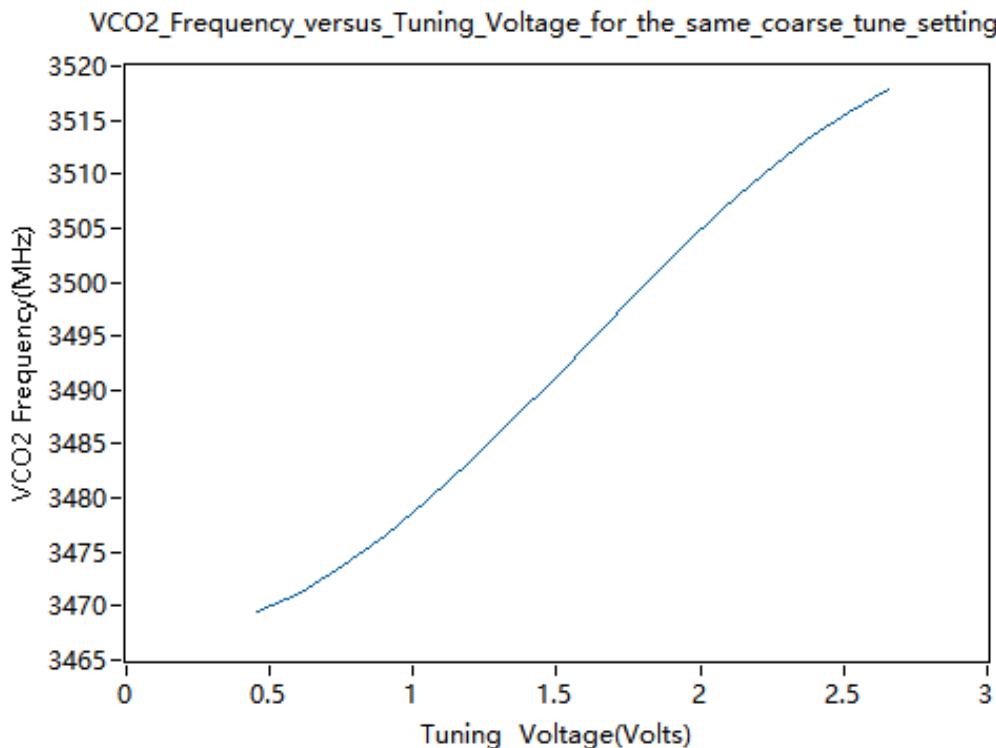

图 37 VCO2 CT\_CAL=127 时, 频率随调谐电压的变化

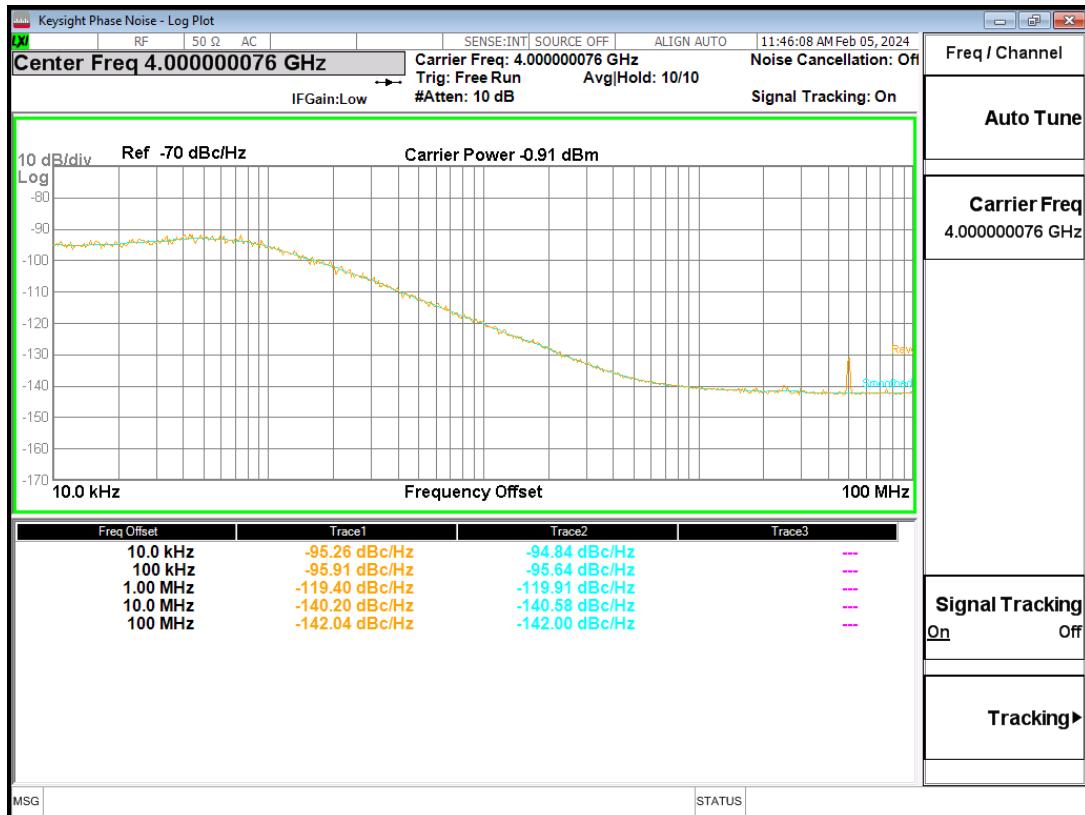

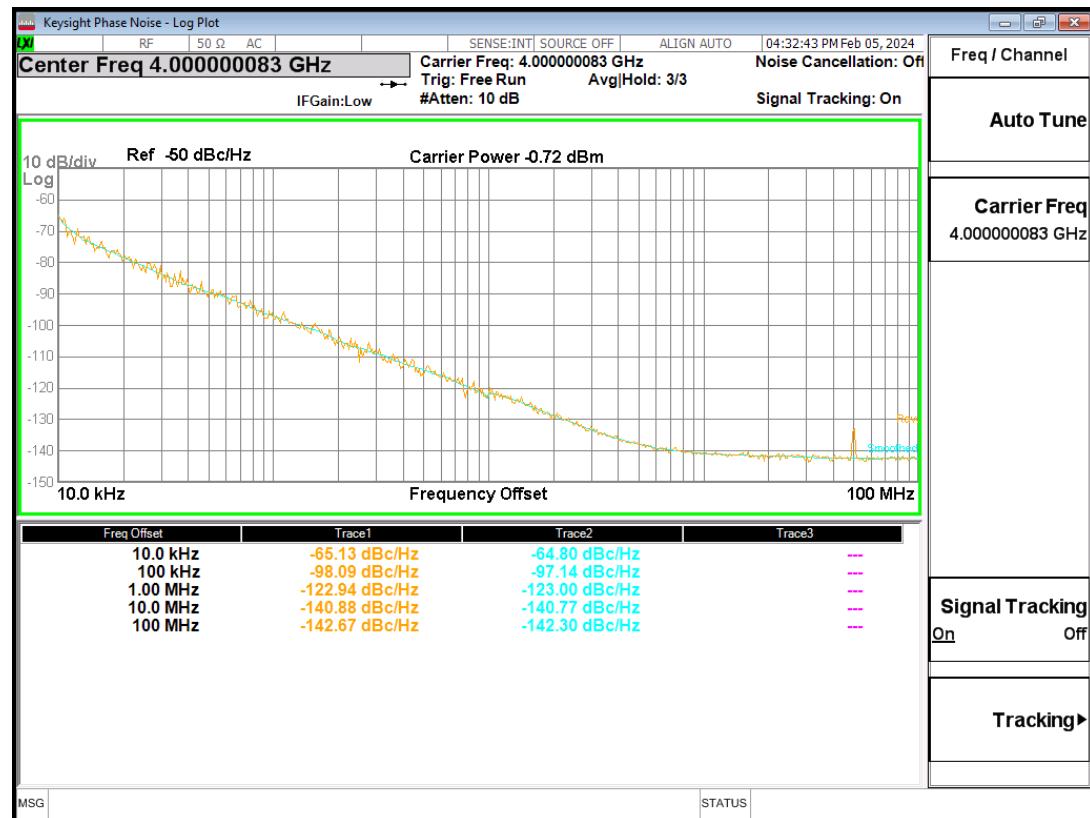

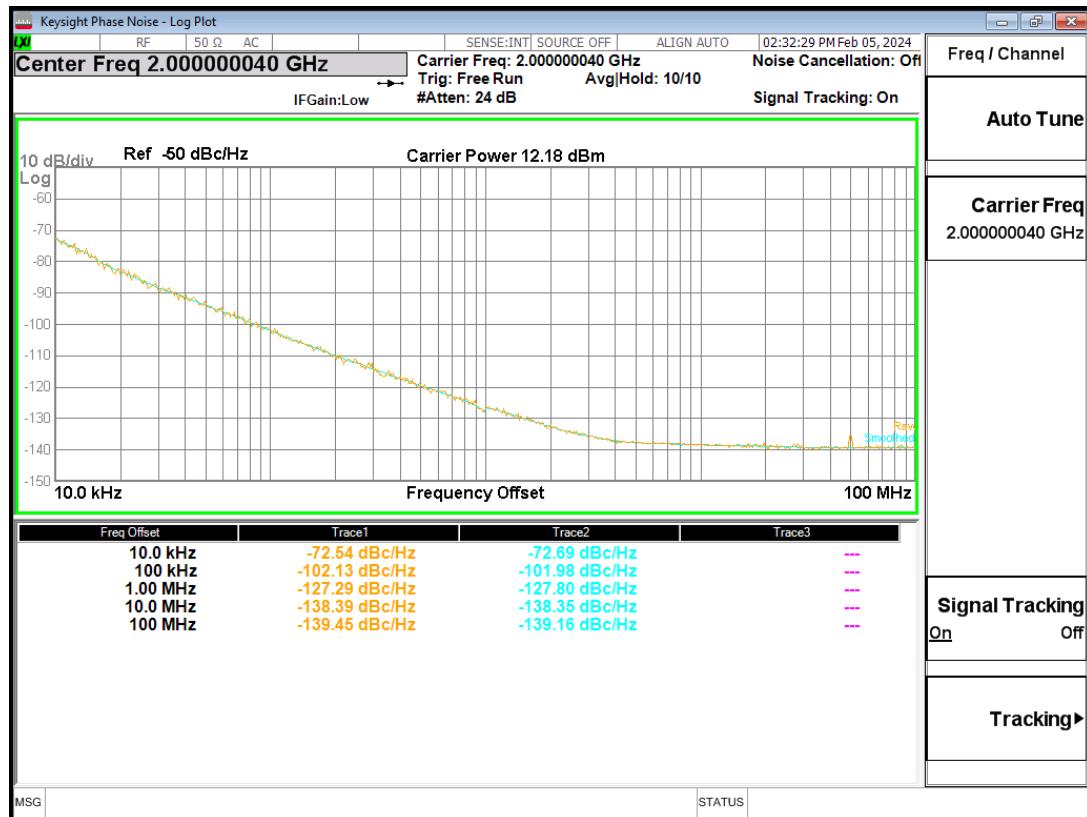

#### 4.3.3 VCO 的相位噪声测试

图 38 VCO0 fvco=1.8GHz 时 VCO 相位噪声

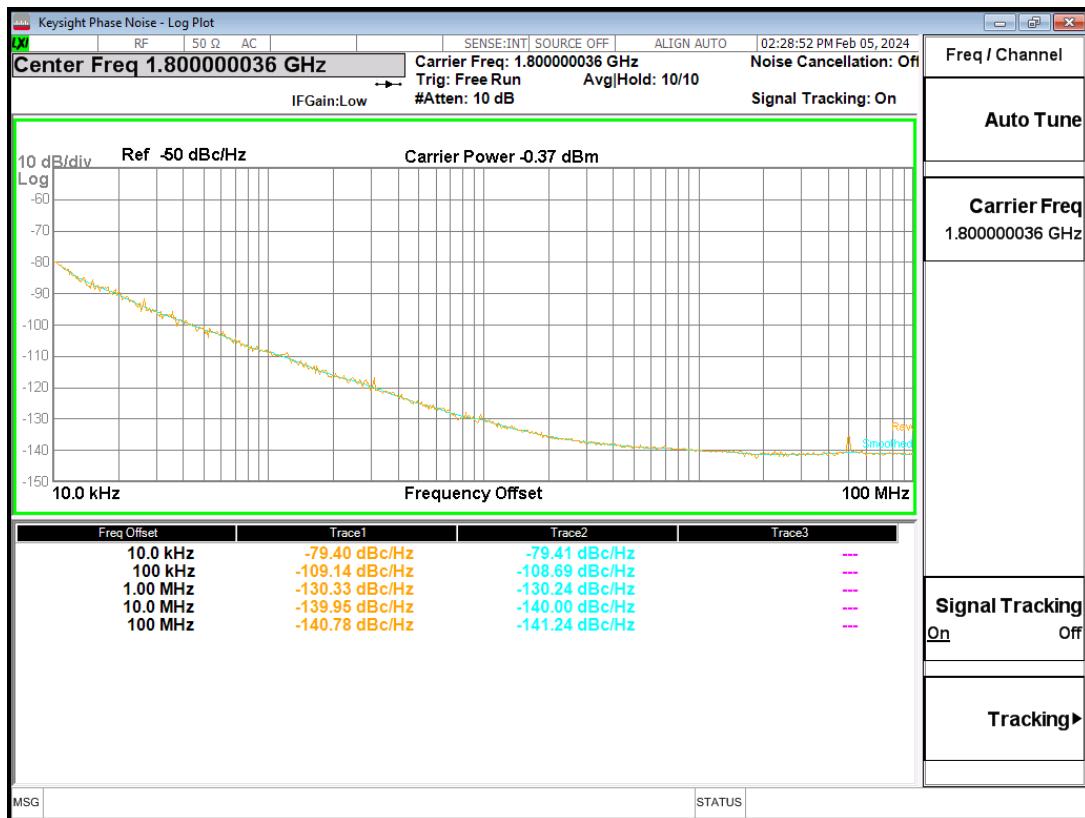

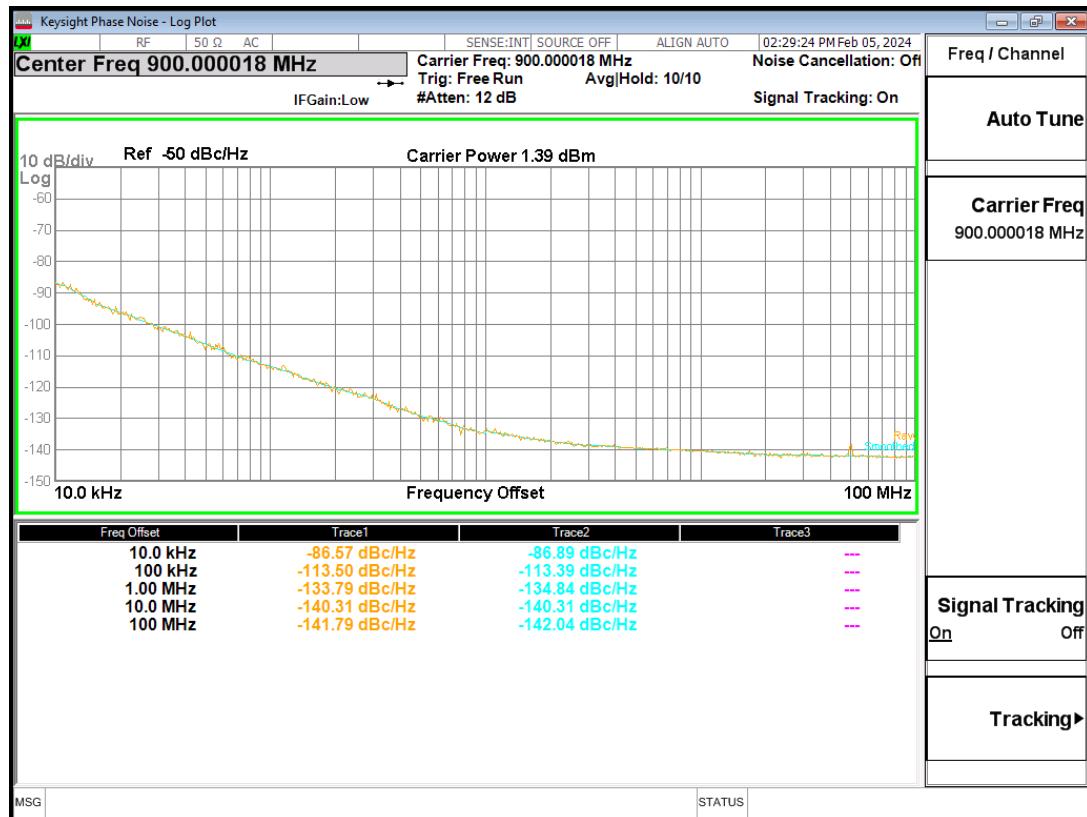

图 39 VC00  $f_{vco}=1.8\text{GHz}$ , 10div 二分频时 VCO 相位噪声图 40 VC01  $f_{vco}=3\text{GHz}$  时 VCO 相位噪声

图 41 VC01  $f_{vco}=3\text{GHz}$ , Lodiv 二分频时 VCO 相位噪声

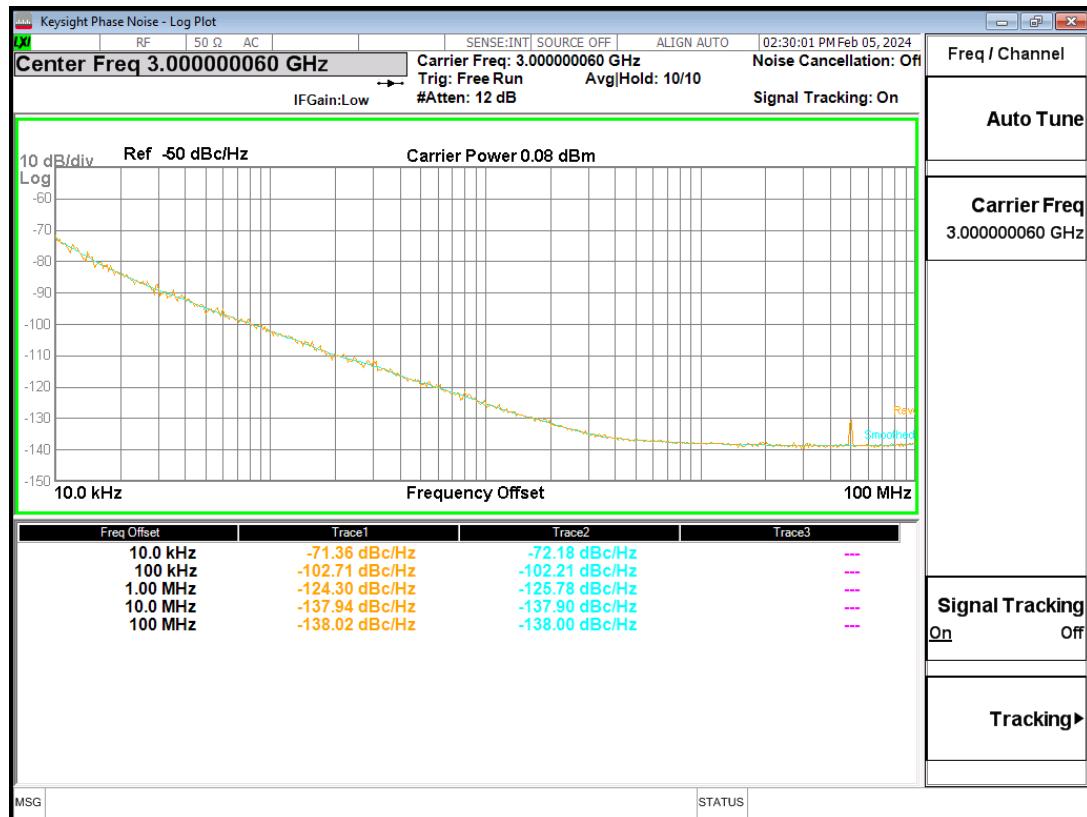

图 42  $f_{VCO} = 4\text{GHz}$  时 VCO 相位噪声

图 43 VCO2  $f_{vco}=4GHz$ , Lodiv 二分频时 VCO 相位噪声

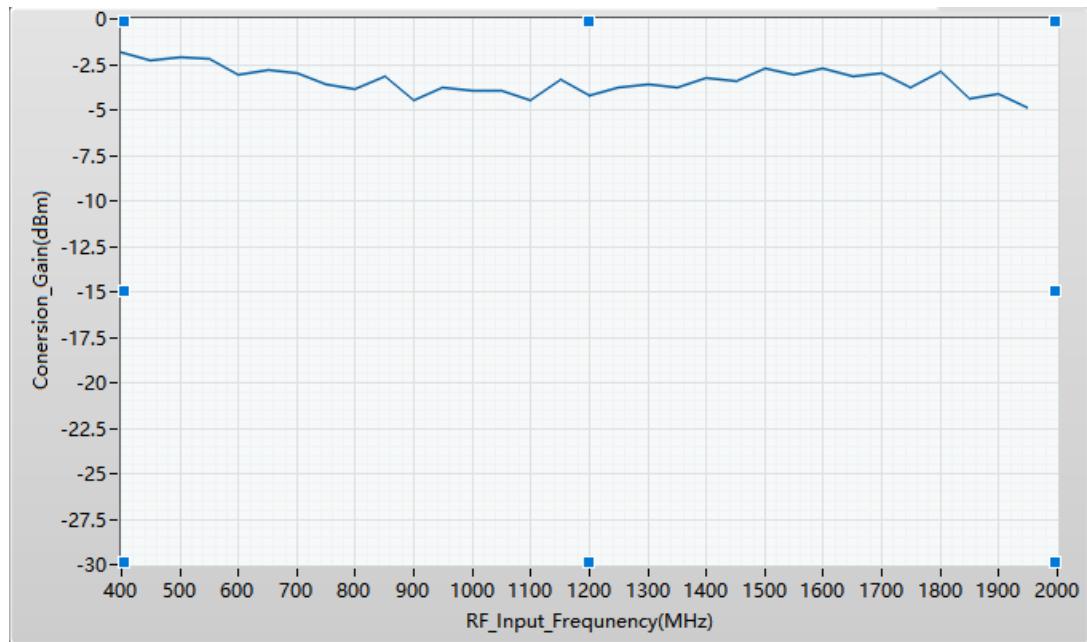

#### 4.4 mixer 的性能测试

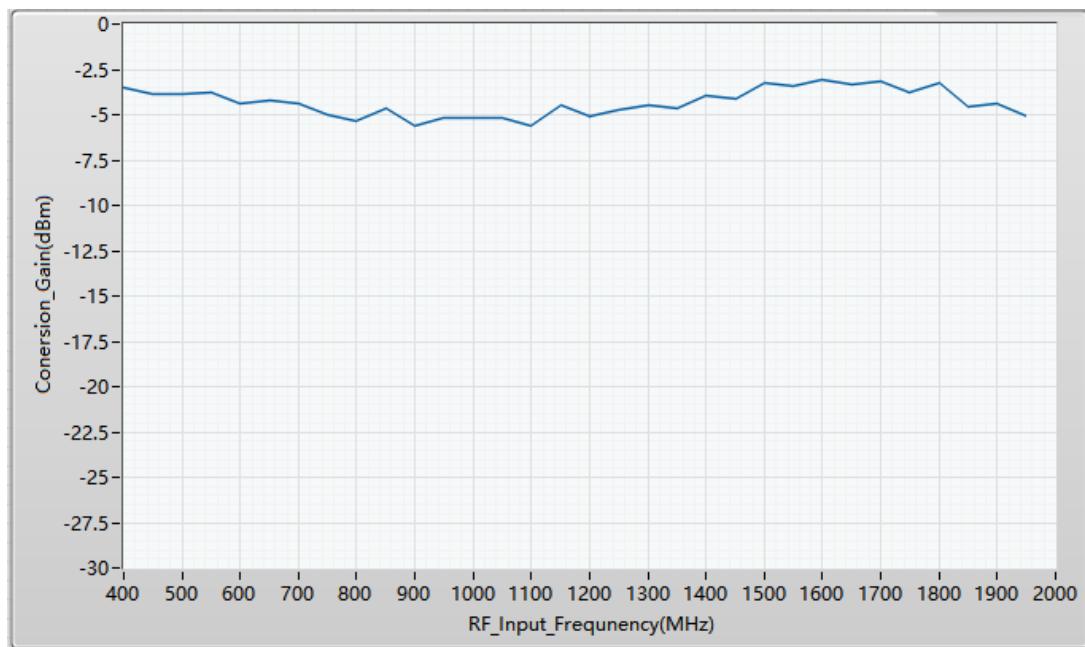

##### 4.4.1 转换增益 Conversion Gain

图 44 RF INPUT 频率 400MHz~2GHz, mixer1 的转换增益

(Conversion Gain of Mixer 1 IF Output=100MHz)

图 45 RF INPUT 频率 400MHz~2GHz , mixer2 的转换增益

(Conversion Gain of Mixer 2 IF Output=100MHz)

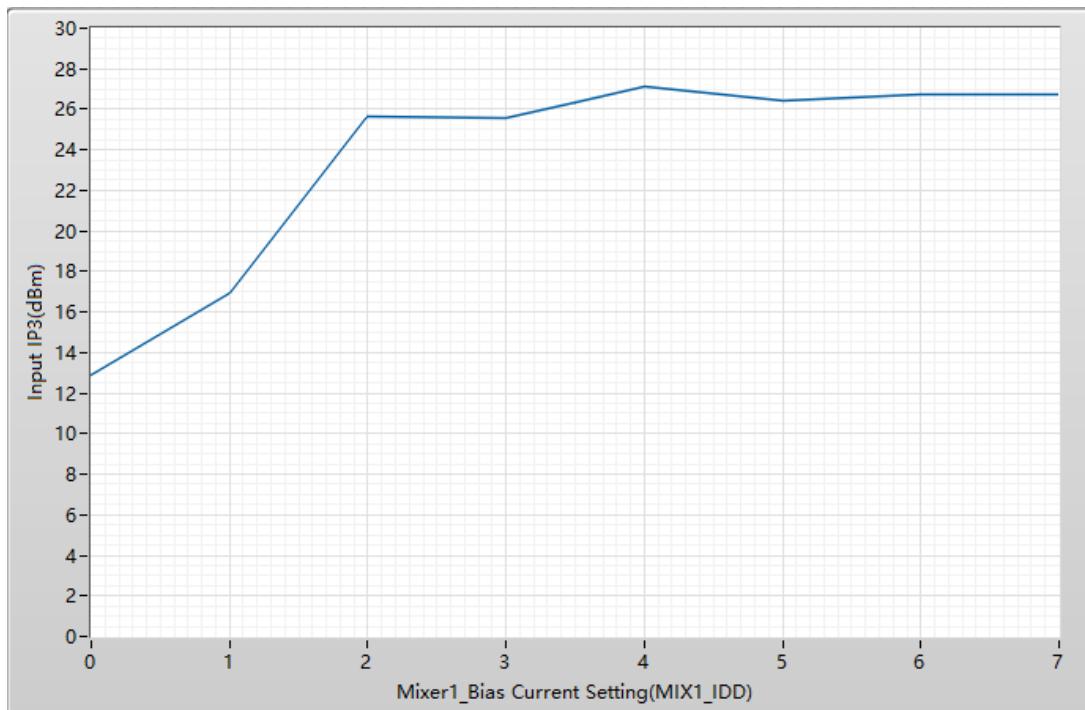

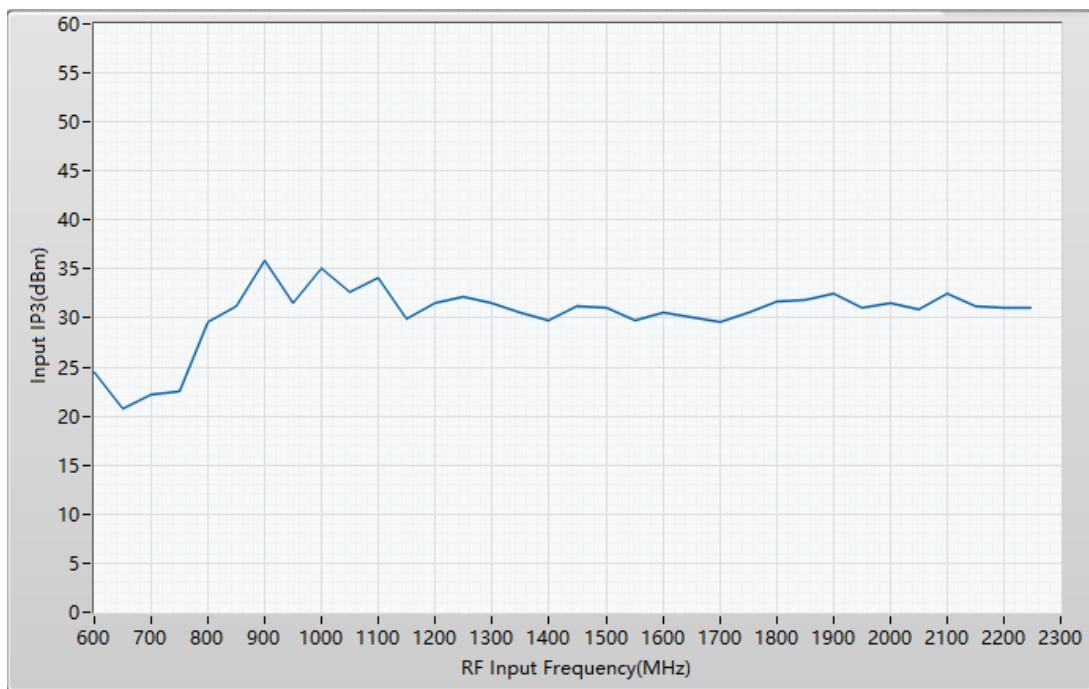

#### 4.4.2 三阶交调 IIP3

图 46 MIX1\_IDD=1~7 时, mixer1 的 IIP3

(Mixer1 Input IP3 Versus bias Current, LO Frequency=1000MHz, IF Output=100MHz)

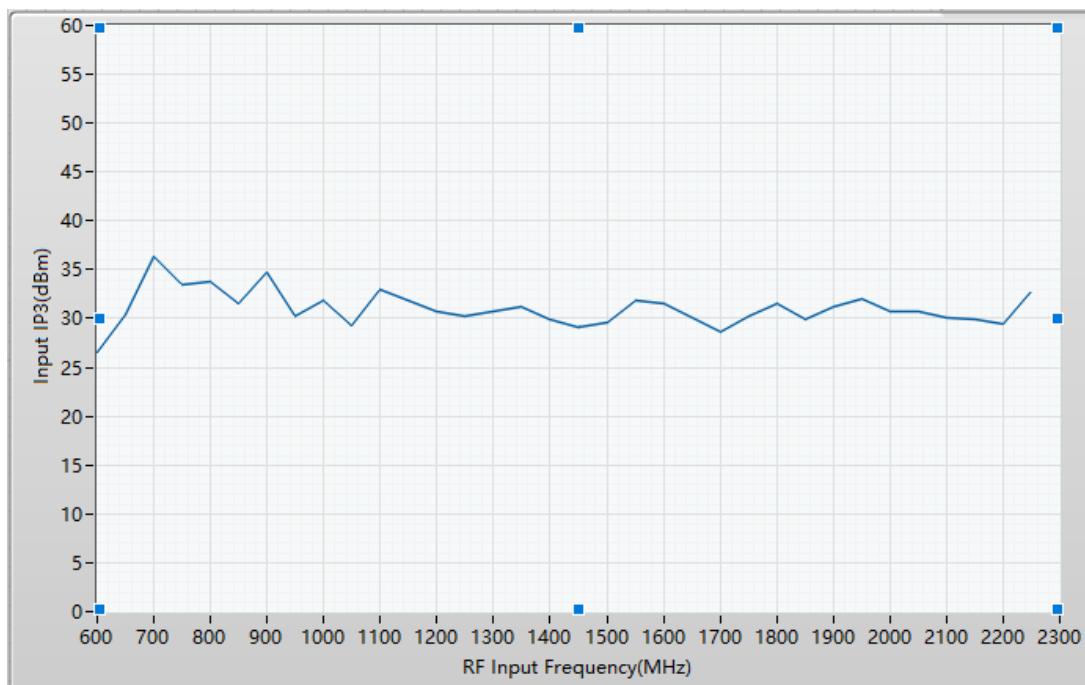

图 47 RF INPUT 频率 500MHz~2.25GHz 时, mixer1 的 IIP3

(Mixer1 Linearity Performance ,MIX\_IDD=5, +3.0V, IF Output=100MHz)

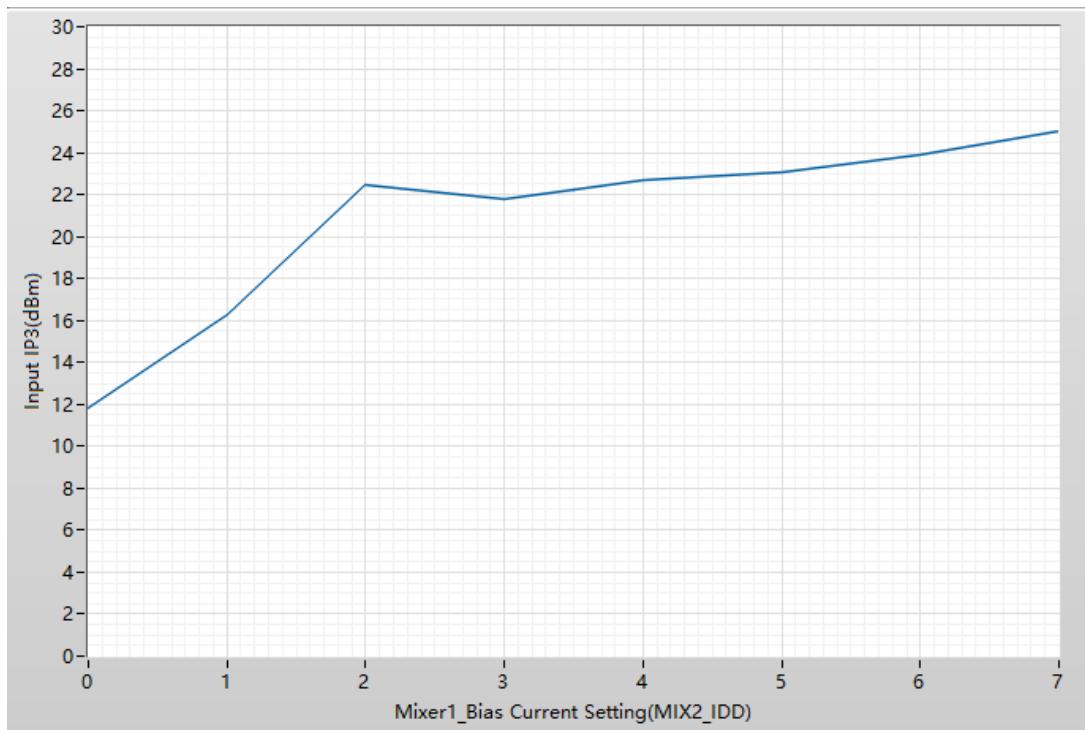

图 48 MIX2\_IDD=1~7 时, mixer1 的 IIP3

(Mixer2 Input IP3 Versus bias Current ,L0 Frequency=1000MHz, IF Output=100MHz)

图 49 RF INPUT 频率 500MHz~2.25GHz 时, mixer2 的 IIP3

(Mixer2Linearity Performance, MIX\_IDD=5, +3.0V, IF Output=100MHz)

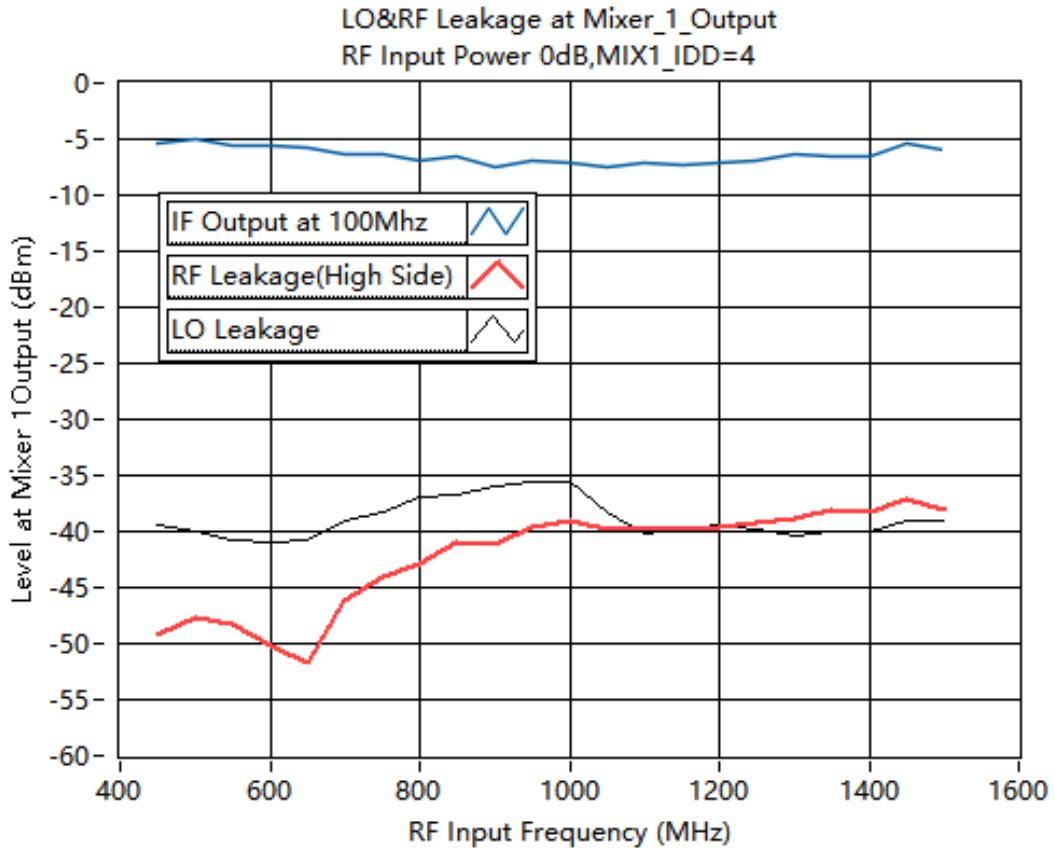

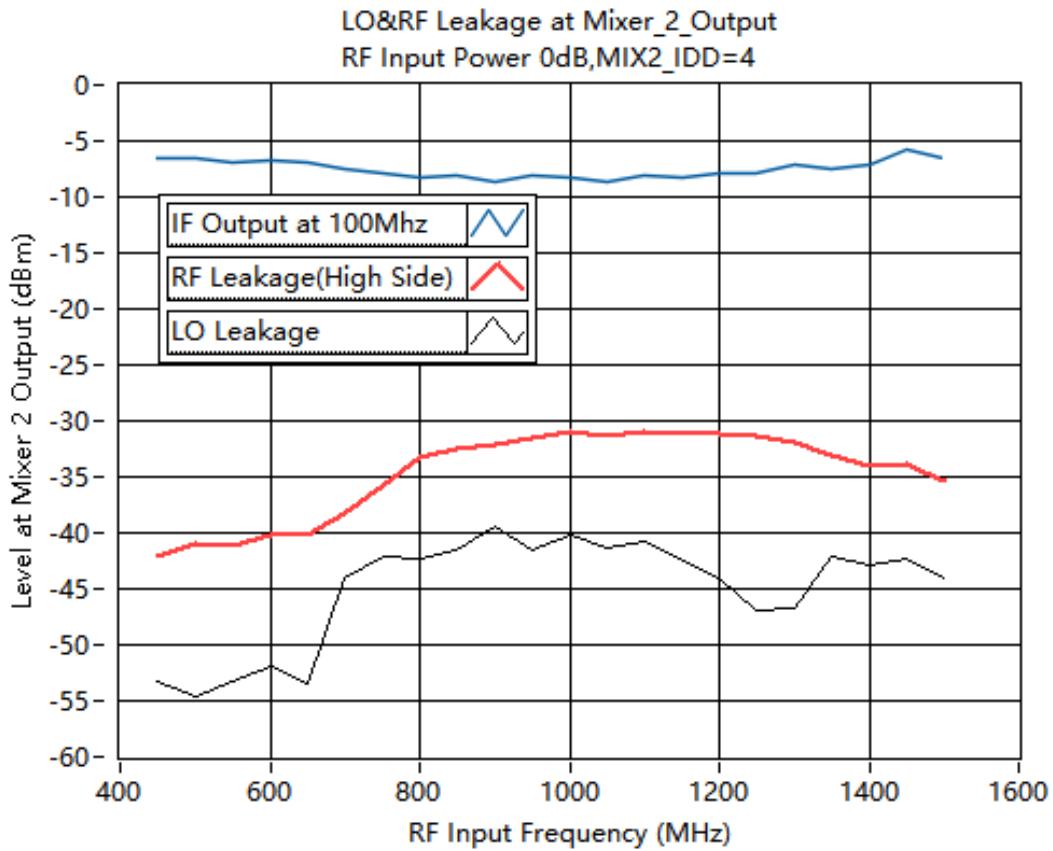

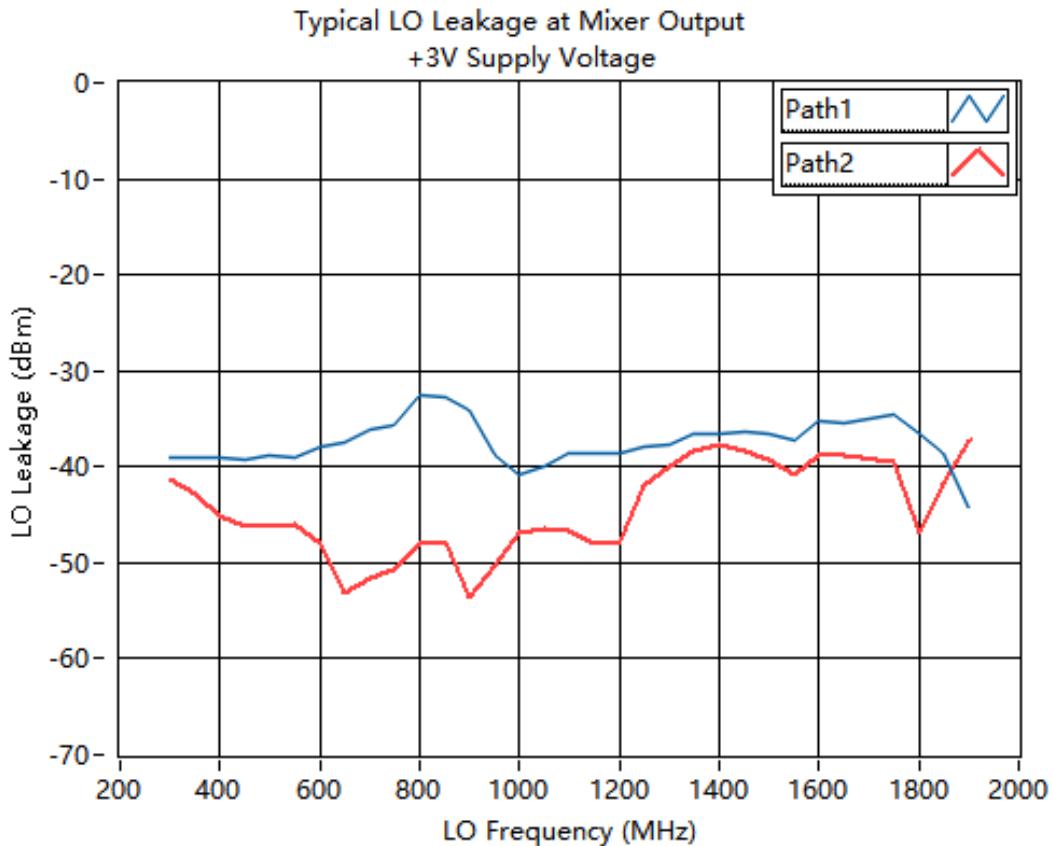

#### 4.4.3 本振 LO 和射频输入在 mixer1 输出口的泄露

图 50 RF INPUT 频率 400MHz~1.6GHz 时, 在 mixer1 输出端的泄露

图 51 RF INPUT 频率 400MHz~1.6GHz 时，在 mixer2 输出端的泄露

图 52 LO 频率 200MHz~2GHz 时，在 mixer 输出端的泄露

## 4.4.4 混频器输入和输出端的输入回波损耗 (S11)

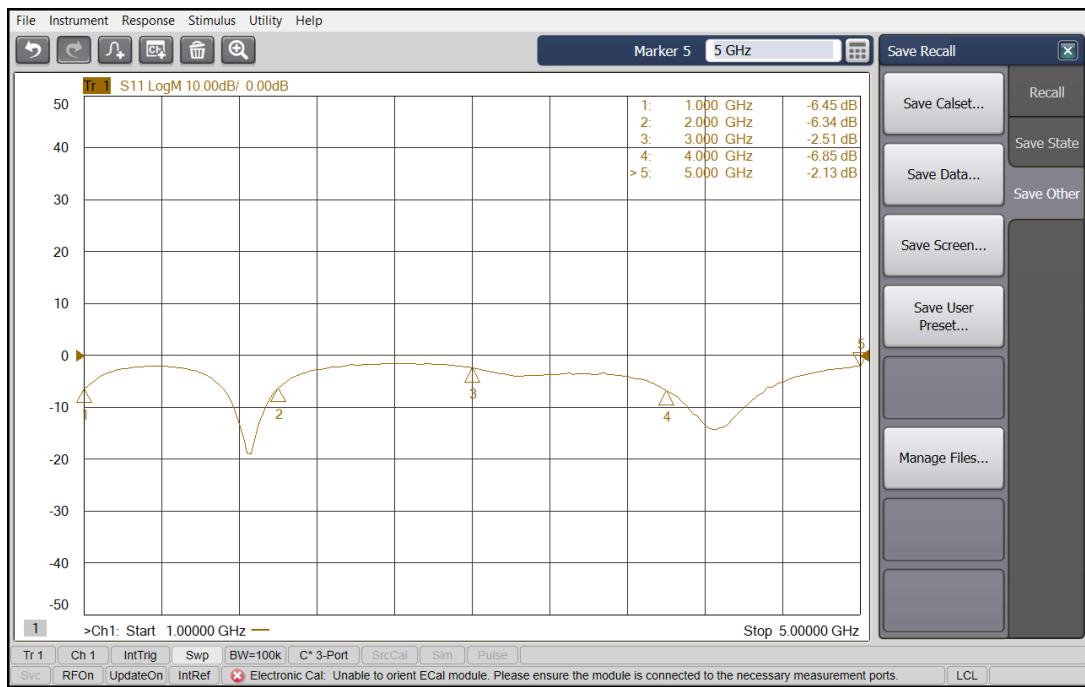

图 53 MIX1 输入端的输入回波损耗 (1~5GHz)

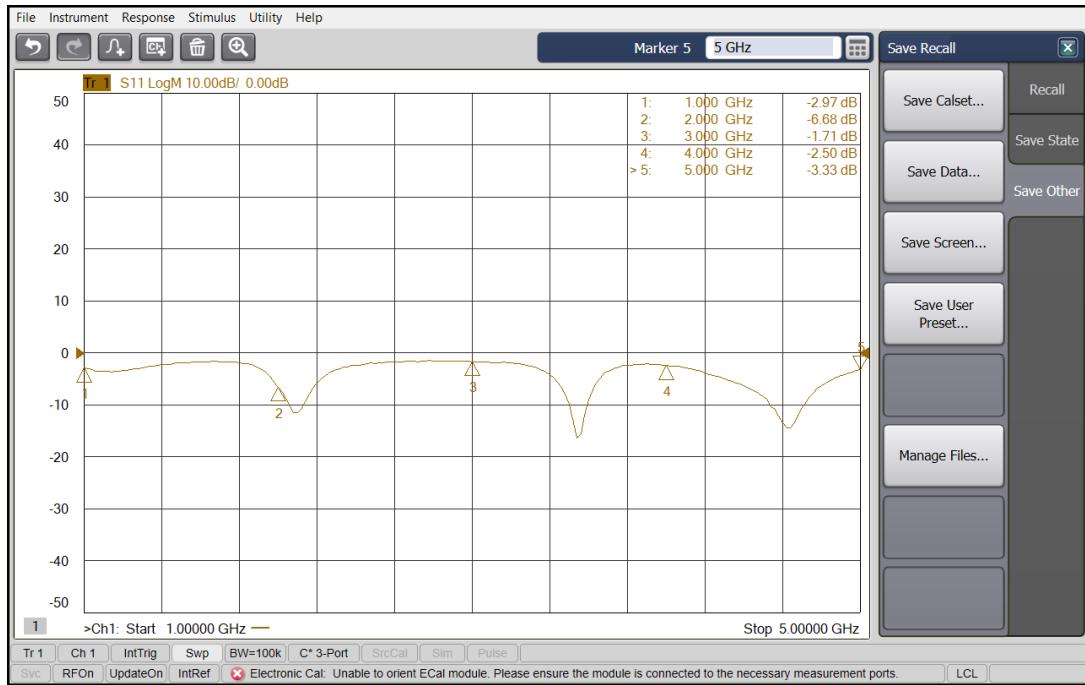

图 54 MIX1 输出端的输入回波损耗 (1~5GHz)

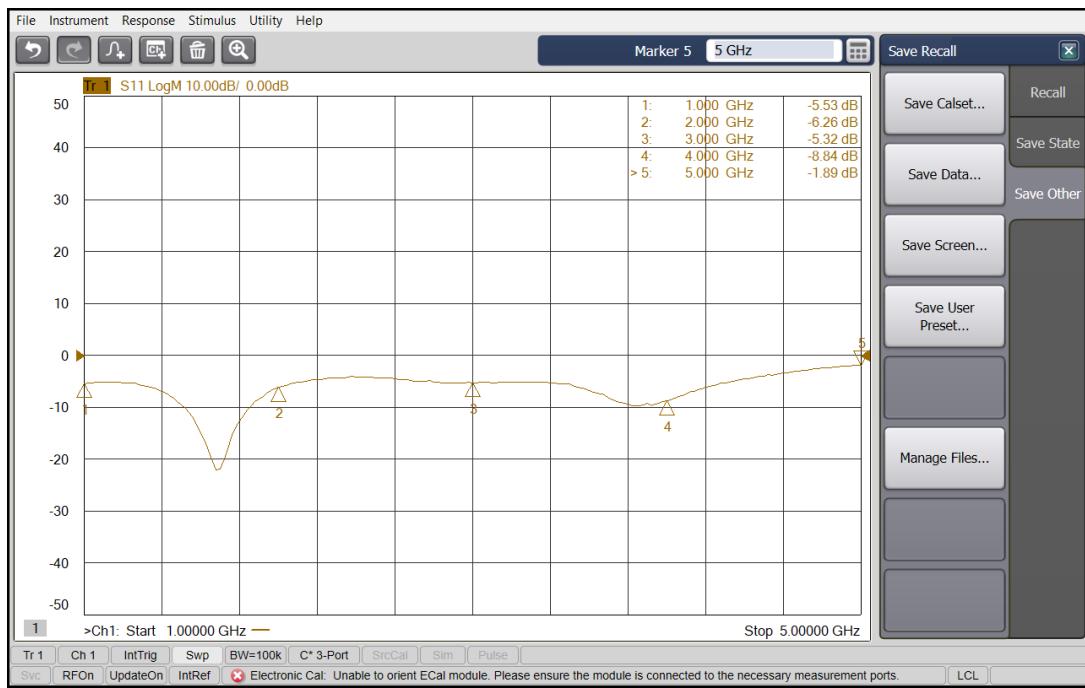

图 55 MIX2 输入端的输入回波损耗 (1~5GHz)

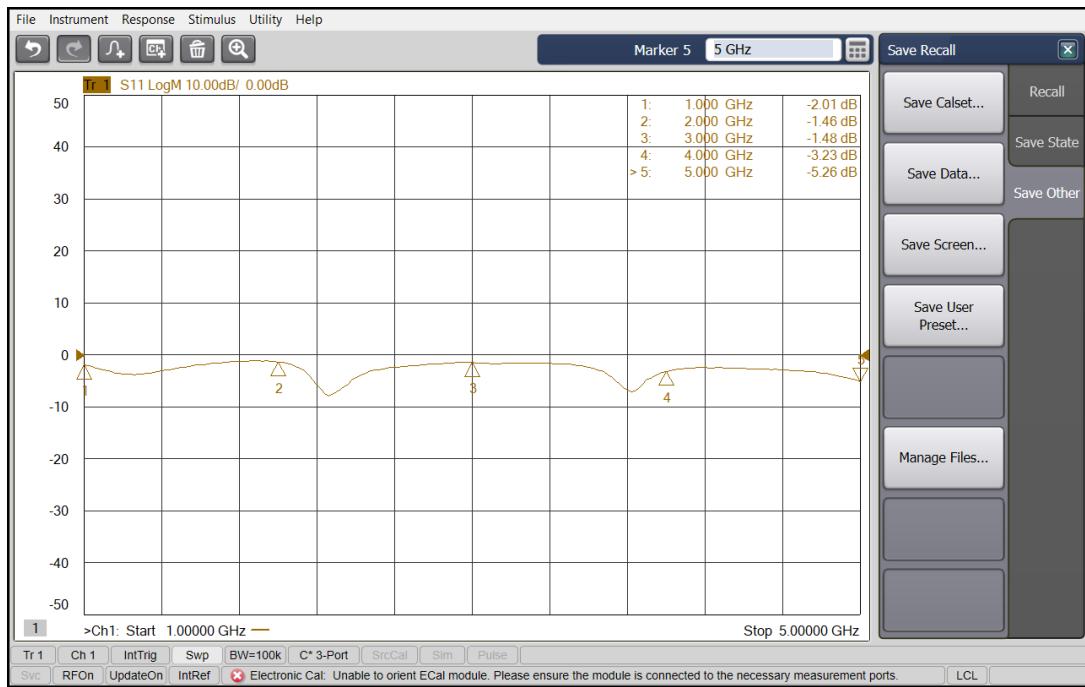

图 56 MIX2 输出端的输入回波损耗 (1~5GHz)

## 5 寄存器列表

| Address | Bits               | Register Name  | Default | Access | Descriptions                                                                                                                                                          |

|---------|--------------------|----------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000   | intreface config A |                |         |        |                                                                                                                                                                       |

|         | 7                  | soft_rst_mir   | 1' b0   | RW     | 软复位                                                                                                                                                                   |

|         | 6                  | en_lsb_mir     | 1' b0   | RW     | SPI 操作时最高位或最低位先发送；默认先发送最高位                                                                                                                                            |

|         | 5                  | en_inc_mir     | 1' b0   | RW     | SPI 多地址操作时地址自动增减方向；默认自减                                                                                                                                               |

|         | 4:3                | Reserved       | 2' h0   | RO     |                                                                                                                                                                       |

|         | 2                  | en_inc         | 1' b0   | RW     | SPI 多地址操作时地址自动增减方向；默认自减                                                                                                                                               |

|         | 1                  | en_lsb         | 1' b0   | RW     | SPI 操作时最高位或最低位先发送；默认先发送最高位                                                                                                                                            |

|         | 0                  | soft_rst       | 1' b0   | RW     | 软复位                                                                                                                                                                   |

| 0x001   | SDI_CTRL           |                |         |        |                                                                                                                                                                       |

|         | 7                  | sipin          | 1' b0   | RW     | 1=ENBL 和 MODE 引脚被忽略并作为 GP05 和 GP06                                                                                                                                    |

|         | 6                  | enbl           | 1' b0   | RW     | 如果 sipin=1 此字段将替换 ENBL 引脚的功能                                                                                                                                          |

|         | 5                  | mode           | 1' b0   | RW     | 如果 sipin_ctrl=1 此字段将替换 MODE 引脚的功能                                                                                                                                     |

|         | 4                  | 4wire_en       | 1' b0   | RW     | 1=4 线 SDI, 即 SDATA 是单向的, SDATA_out 被映射到 GP04                                                                                                                          |

|         | 3                  | addr           | 1' b0   | RW     | 1=将 ADD1, ADD2 引脚映射到 SPI 地址 {GP02, GP01, reg_addr} 的输入; 这提供了 4 个可能的设备地址。                                                                                              |

|         | 2                  | gpo_gate       | 1' b0   | RW     | GPO 门控使能信号; 0=GPO 输出为 0; 1=输出 p1gpo_val 或者 p2gpo_val。 (此处相应引脚作为 GPO 功能输出的优先级低于用作其他功能引脚的优先级, 比如 GP05 和 GP06 优先作为 ENBL 和 MODE 功能引脚, 只有当 sipin=1 时, 这些引脚才可以作为 GPO 输出功能。) |

|         | 1                  | lock_gate      | 1' b0   | RW     | 将 LOCK 标志发送到 GP04。                                                                                                                                                    |

|         | 0                  | Reserved       | 1' b0   | RO     |                                                                                                                                                                       |

| 0x002   | PATH1GPO - VAL     |                |         |        |                                                                                                                                                                       |

|         | 7:6                | Reserved       | 2' b0   | RO     |                                                                                                                                                                       |

|         | 5:0                | p1gpo_val[5:0] | 6' b0   | RW     | 路径 1 的 GPO, 1 = 高, 0 = 低。 MODE 引脚或 SDI 字段控制是否使用 p1gpo_val 或 p1gpo_val 中的值。                                                                                            |

| 0x003   | PATH2GPO - VAL     |                |         |        |                                                                                                                                                                       |

|         | 7:6                | Reserved       | 2' b0   | RO     |                                                                                                                                                                       |

| Address | Bits               | Register Name      | Default | Access | Descriptions                                                                           |

|---------|--------------------|--------------------|---------|--------|----------------------------------------------------------------------------------------|

|         | 5:0                | p2gpo_val[5:0]     | 6' b0   | RW     | 路径 2 的 GPO, 1 = 高, 0 = 低。<br>MODE 引脚或 SDI 字段控制是否使用 p1gpo_val 或 p1gpo_val 中的值。          |

| 0x004   | ANA_EN_CTRL_MANUAL |                    |         |        |                                                                                        |

|         | 7                  | en_vco_ldo         | 1' b1   | RW     | VCO 的 LDO 使能                                                                           |

|         | 6                  | en_ndiv_ldo        | 1' b1   | RW     | N 分频器的 LDO 使能                                                                          |

|         | 5                  | en_ref             | 1' b1   | RW     | REF 使能                                                                                 |

|         | 4                  | ana_ctrl_manual_en | 1' b0   | RW     | 模拟模块使能信号手动模式使能                                                                         |

|         | 3                  | en_cp_manual       | 1' b1   | RW     | CP 手动使能, 在 ana_ctrl_manual_en=1 时有效                                                    |

|         | 2                  | en_ndiv_manual     | 1' b1   | RW     | N 分频器手动使能, 在 ana_ctrl_manual_en=1 时有效                                                  |

|         | 1                  | en_vco_manual      | 1' b1   | RW     | VCO 手动使能, 在 ana_ctrl_manual_en=1 时有效                                                   |

|         | 0                  | Reserved           | 1' b0   | RO     |                                                                                        |

| 0x005   | PLL_CTRL1          |                    |         |        |                                                                                        |

|         | 7                  | pllst              | 1' b0   | RW     | PLL 待机模式:<br>1: 始终开启 VCO、CP、Ndvi 的使能信号;<br>0: VCO、CP、Ndvi 的使能信号由 enb1 寄存器或者 ENBL 引脚控制; |

|         | 6                  | Reserved           | 1' b1   | RO     |                                                                                        |

|         | 5                  | rdiv_rstn          | 1' b1   | RW     | RDIV 的复位信号, 1 工作, 0 复位。                                                                |

|         | 4:3                | Reserved           | 2' b0   | RO     |                                                                                        |

|         | 2                  | relok              | 1' b0   | W1C    | 自清除位。当此位设置为高时, 它会触发 PLL 的重新锁定, 然后清除 (Rdiv_clk, 作为清零时钟)                                 |

|         | 1                  | ref_sel            | 1' b0   | RW     | Ref 有单端和差分输入, 0 时选择单端输入; 1 时选择差分输入。                                                    |

|         | 0                  | Reserved           | 1' b0   | RO     |                                                                                        |

|         | PLL_CTRL2          |                    |         |        |                                                                                        |

| 0x006   | 7:0                |                    |         |        |                                                                                        |

|         | 7:0                | tvco[7:0]          | 8' h07  | RW     | VCO 预热时间, 时间为 tvco*2*(ref_div_ctrl+1)*2*(meas_time_ctrl+1)*2*Rdiv/fref                 |

| 0x007   | R_DIVDER_CTRL1     |                    |         |        |                                                                                        |

|         | 7                  | Reserved           | 1' b0   | RO     |                                                                                        |

| 0x007   | 6:0                |                    |         |        |                                                                                        |

|         | 6:0                | clkdiv[6:0]        | 7' h5   | RW     | 为 divby =0 时, fRdivout=fref/clkdiv (clkdiv=2^127), 模拟实际有 8bit 控制 (2^255)。              |

| 0x008   | LO_CFG_COM         |                    |         |        |                                                                                        |

|         | 7:3                | Reserved           | 5' b0   | RO     |                                                                                        |

| Address | Bits                   | Register Name            | Default | Access | Descriptions                                                         |

|---------|------------------------|--------------------------|---------|--------|----------------------------------------------------------------------|

| 0x009   | 2                      | en_lo_div_ldo            | 1' b1   | RW     | Lo 分频器的 LDO 使能信号                                                     |

|         | 1                      | en_lo_div                | 1' b1   | RW     | Lo 分频器的使能信号                                                          |

|         | 0                      | ext_lo_en                | 1' b0   | RW     | 外部输入本振使能信号, 为 0 时关闭; 为 1 时, 开启。                                      |

| 0x00A   | LO_DIV_CML_BUFFER_CFG1 |                          |         |        |                                                                      |

|         | 7:6                    | Reserved                 | 2' b0   | RO     |                                                                      |

|         | 5                      | enn_filter_lod_ivmuxbias | 1' b1   | RW     |                                                                      |

|         | 4                      | enn_filter_lod_ivmuxvcom | 1' b1   | RW     |                                                                      |

|         | 3:0                    | lodivmux_vcom_cur[3:0]   | 4' hA   | RW     | Lodiv CMLbuffer 配置                                                   |

| 0x00B   | LO_DIV_CML_BUFFER_CFG2 |                          |         |        |                                                                      |

|         | 7                      | Reserved                 | 1' b0   | RO     |                                                                      |

|         | 6:4                    | lodivmux_bias_cur[2:0]   | 3' h7   | RW     |                                                                      |

|         | 3                      | Reserved                 | 1' b0   | RO     |                                                                      |

|         | 2:0                    | lodivmux_load[2:0]       | 3' h7   | RW     |                                                                      |

| 0x00C   | P1_LO_CFG              |                          |         |        |                                                                      |

|         | 7:3                    | Reserved                 | 5' b0   | RO     |                                                                      |

|         | 2:0                    | p1_lo_div[2:0]           | 3' b0   | RW     | path1 LO 分频器配置字, 分频器范围<br>(2^64) ; div_val =<br>2^(p1_lo_div[2:0]+1) |

| 0x00D   | P2_LO_CFG              |                          |         |        |                                                                      |

|         | 7:3                    | Reserved                 | 5' b0   | RO     |                                                                      |

|         | 2:0                    | p2_lo_div[2:0]           | 3' b0   | RW     | path2 LO 分频器配置字, 分频器范围<br>(2^64) ; div_val =<br>2^(p2_lo_div[2:0]+1) |

| 0x00E   | P1_N_DIV_CFG1          |                          |         |        |                                                                      |

|         | 7:3                    | Reserved                 | 5' b0   | RO     |                                                                      |

|         | 2:0                    | p1_n_div[10:8]           | 3' h0   | RW     | path1 NDIV 的分频器设置 72~2047                                            |

| 0x00F   | P1_N_DIV_CFG2          |                          |         |        |                                                                      |

|         | 7:0                    | p1_n_div[7:0]            | 8' h74  | RW     | path1 NDIV 的分频器设置 72~2047                                            |

|         | P2_N_DIV_CFG1          |                          |         |        |                                                                      |

| 0x010   | 7:3                    | Reserved                 | 5' b0   | RO     |                                                                      |

|         | 2:0                    | p2_n_div[10:8]           | 3' h0   | RW     | path2 NDIV 的分频器设置 72~2047                                            |

| 0x011   | P2_N_DIV_CFG2          |                          |         |        |                                                                      |

|         | 7:0                    | p2_n_div[7:0]            | 8' h74  | RW     | path2 NDIV 的分频器设置 72~2047                                            |

| 0x012   | P1_PRESCALER_CONFIG    |                          |         |        |                                                                      |

|         | 7:4                    | Reserved                 | 4' b0   | RO     |                                                                      |

| Address | Bits               | Register Name                     | Default | Access | Descriptions                                                                                              |

|---------|--------------------|-----------------------------------|---------|--------|-----------------------------------------------------------------------------------------------------------|

|         | 3:0                | p1_prescaler_1<br>oad_config[3:0] | 4' h8   | RW     | Prescaler 负载配置。                                                                                           |

| 0x012   | P2_PRESCALER_COFIG |                                   |         |        |                                                                                                           |

|         | 7:4                | Reserved                          | 4' b0   | RO     |                                                                                                           |

|         | 3:0                | p2_prescaler_1<br>oad_config[3:0] | 4' h8   | RW     | Prescaler 负载配置。                                                                                           |

| 0x013   | BG_PTAT_CUR        |                                   |         |        |                                                                                                           |

|         | 7:5                | Reserved                          | 3' b0   | RO     |                                                                                                           |

|         | 4                  | en_bandgap                        | 1' b1   | RW     | 使能 bandgap 模块                                                                                             |

|         | 3:0                | bg_ptat_cur[3:0]                  | 4' h9   | RW     | 修调 ZTC 电流的控制字, 如 ZTC 电流正温系数, 则减小该控制字; 如 ZTC 电流负温系数, 则增大该控制字;<br>I_BgPtatCur = 4.5uA *<br>BgPtatCur < 3:0> |

| 0x014   | BG_PTAT_VREF_CUR   |                                   |         |        |                                                                                                           |

|         | 7:6                | Reserved                          | 2' b0   | RO     |                                                                                                           |

|         | 5:0                | bg_ptat_vref_c<br>ur[5:0]         | 6' h20  | RW     | 修调产生带隙基准的电压的控制字;<br>如带隙基准正温系数, 则减小该控制字; 如带隙基准负温系数, 则增大该控制字; I_BgPtatCur = 2.2uA *<br>BgPtatVrefCur < 5:0> |

| 0x015   | VCO_CUR1           |                                   |         |        |                                                                                                           |

|         | 7:4                | vco_bg_ptat_cu<br>r50u[3:0]       | 4' h8   | RW     | IBiasPtat50u =<br>VcoBgtatCur50u < 3:0> * 6.4uA                                                           |

|         | 3:0                | vco_bias_cur25<br>u_e[3:0]        | 4' h8   | RW     | I_VcoBiasCur25u_E =<br>VcoBiasCur25u_E < 3:0> * 3.25uA                                                    |

| 0x016   | VCO_CUR2           |                                   |         |        |                                                                                                           |

|         | 7:4                | vco_bias_cur25<br>u_f[3:0]        | 4' h8   | RW     | I_VcoBiasCur25u_F =<br>VcoBiasCur25u_F < 3:0> * 3.25uA                                                    |

|         | 3:0                | vco_bias_cur50<br>u_a[3:0]        | 4' h8   | RW     | I_VcoBiasCur50u_A =<br>VcoBiasCur50u_A < 3:0> * 6.5uA                                                     |

| 0x017   | ZTC_CUR3           |                                   |         |        |                                                                                                           |

|         | 7:4                | bias_cur25u_g[<br>3:0]            | 4' h8   | RW     | ZTC 电流, I_BiasCur25u_G = 3.25uA *<br>BiasCur25u_G < 3:0>                                                  |

|         | 3:0                | bias_cur25u_h[<br>3:0]            | 4' h8   | RW     | ZTC 电流, I_BiasCur25u_N = 3.25uA *<br>BiasCur25u_N < 3:0>                                                  |

| 0x018   | ZTC_CUR3           |                                   |         |        |                                                                                                           |

|         | 7:4                | ldo_bias_cur50<br>u_b[3:0]        | 4' h5   | RW     | ZTC 电流, I_Bias50uNB = 6.5uA *<br>BiasCur50u_B < 3:0>                                                      |

| Address | Bits         | Register Name           | Default | Access | Descriptions                                                                                                                     |

|---------|--------------|-------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------|

|         | 3:0          | ldo_bias_cur50u_c[3:0]  | 4' h5   | RW     | ZTC 电流, IBias50uNC=6.5uA*<br>BiasCur50u_C<3:0>                                                                                   |

| 0x019   | ZTC_CUR3     |                         |         |        |                                                                                                                                  |

|         | 7:4          | bias_cur50u_d[3:0]      | 4' h8   | RW     | ZTC 电流, IBias50uND=6.5uA*<br>bias_cur50u_d[3:0]                                                                                  |

|         | 3:0          | bias_cur100u_d[3:0]     | 4' h8   | RW     | ZTC 电流, IBias100uND =13uA*<br>BiasCur100u_B<3:0>                                                                                 |

| 0x01A   | ZTC_CUR4     |                         |         |        |                                                                                                                                  |

|         | 7:4          | ref_bias_cur100u_b[3:0] | 4' hf   | RW     | 参考时钟输入级, 选择差分时的电流<br>配置 ZTC 电流, IBias100uNB =13uA*<br>BiasCur100u_B<3:0>                                                         |

|         | 3:0          | lo_bias_cur100u_c[3:0]  | 4' hf   | RW     | ZTC 电流, IBias100uNC =13uA*<br>BiasCur100u_B<3:0>;<br>(需要配置为 4 'h8)                                                               |

| 0x01B   | CP_CUR_CTRL1 |                         |         |        |                                                                                                                                  |

|         | 7            | cp_cur_select_bias3n    | 1' b0   | RW     | 为 0 时, CP 的 BIAS3N (30uA) 由<br>bandgap 产生; 为 1 时, CP 的 BIAS3N<br>(30uA) 由 ZTC 电流 ICPBias25uNA 产<br>生                             |

|         | 6            | cp_cur_select_bias4n    | 1' b0   | RW     | 为 0 时, CP 的 BIAS3N (30uA) 由<br>bandgap 产生; 为 1 时, CP 的 BIAS3N<br>(30uA) 由 ZTC 电流 ICPBias25uNA 产<br>生                             |

| 0x01C   | 5:0          | cp_cur_offset[5:0]      | 6' b0   | RW     | Charge 电流的 offset 配置, Ioffset= CpcCurOffset[5:0]*11.7uA。注意默<br>认配置为<000000>, 是关了 offset 电<br>流的, 如果测试时发现 Spur 大, 可以<br>打开这个配置调试。 |

|         | CP_CUR_CTRL1 |                         |         |        |                                                                                                                                  |

|         | 7:4          | cp_bias_cur25u_a[3:0]   | 4' h9   | RW     | ZTC 电流, ICPBias25uNA=3.25uA*<br>cp_bias_cur25u_a<3:0>, 给 CP 提供<br>BIAS3N 偏置的电流, 30uA<br>(cp_cur_select_bias3n=1 有效)              |

| 0x01D   | 3:0          | cp_bias_cur25u_b[3:0]   | 4' h9   | RW     | ZTC 电流, ICPBias25uNA=3.25uA*<br>cp_bias_cur25u_b<3:0>, 给 CP 提供<br>BIAS3N 偏置的电流, 30uA<br>(cp_cur_select_bias4n=1 有效)              |

|         | CP_CUR_CTRL2 |                         |         |        |                                                                                                                                  |

|         | 7:4          | cp_bias_cur100u_a[3:0]  | 4' h8   | RW     | ZTC 电流, IBias100uNA =13uA*<br>cp_bias_cur100u_a[3:0], 给 CP 提供<br>CPBIAS 提供偏置的电流, 100uA<br>(cp_cur_select_cp_bias=1 有效)           |

| Address | Bits            | Register Name         | Default | Access | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------------|-----------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 3               | cp_cur_select_cp_bias | 1' b0   | RW     | 为 0 时, CP 的 CPBIAS (100uA) 由 bandgap 产生; 为 1 时, CP 的 CPBIAS (100uA) 由 ZTC 电流 IBias100uNA 产生。                                                                                                                                                                                                                                                                                                                                                  |

|         | 2:0             | cp_cur_bg[2:0]        | 3' b0   | RW     | 当选择 banggap 产生的电流作为 CP 的电流时, ICPBIAS=100uA+25uA*cp_cur_bg[2:0]; (需要配置为3' h4)                                                                                                                                                                                                                                                                                                                                                                  |

| 0x01E   | P1_PFD_CUR_CTRL |                       |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 7:5             | p1_cp_cur_pfd[2:0]    | 3' h7   | RW     | path1 Chargepump 的电流控制字                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 4               | p1_pfd_hgh_impdnc     | 1' b1   | RW     | path1 CP 工作模式控制字<br>p1_pfd_hgh_impdnc=0 ,<br>p1_pfd_mode[1:0]=xx, CP 为高阻模式, UP=1, DN=0, UP 和 DN 电流都关闭;<br>p1_pfd_hgh_impdnc=1 ,<br>p1_pfd_mode[1:0]=00, CP 为正常工作模式;<br>p1_pfd_hgh_impdnc=1 ,<br>p1_pfd_mode[1:0]=01, CP 为测试模式, UP=0, DN=0, UP 电流开启, 测试 UP 电流;<br>p1_pfd_hgh_impdnc=1 ,<br>p1_pfd_mode[1:0]=10, CP 为测试模式, UP=1, DN=1, DN 电流开启, 测试 DN 电流;<br>p1_pfd_hgh_impdnc=1 ,<br>p1_pfd_mode[1:0]=11, CP 为高阻模式, UP=1, DN=0, UP 和 DN 电流都关闭; |

|         | 3:2             | p1_pfd_mode[1:0]      | 2' b0   | RW     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 1:0             | Reserved              | 2' b0   | RO     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | P2_PFD_CUR_CTRL |                       |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x01F   | 7:5             | p2_cp_cur_pfd[2:0]    | 3' h7   | RW     | path2 Chargepump 的电流控制字                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 4               | p2_pfd_hgh_impdnc     | 1' b1   | RW     | path2 CP 工作模式控制字<br>p2_pfd_hgh_impdnc=0 ,<br>p2_pfd_mode[1:0]=xx, CP 为高阻模式, UP=1, DN=0, UP 和 DN 电流都关闭;<br>p2_pfd_hgh_impdnc=1 ,<br>p2_pfd_mode[1:0]=00, CP 为正常工作模式;                                                                                                                                                                                                                                                                           |

|         | 3:2             | p2_pfd_mode[1:0]      | 2' b0   | RW     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address            | Bits | Register Name                 | Default | Access | Descriptions                                                                                                                                                                                                                                                                                |

|--------------------|------|-------------------------------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |      |                               |         |        | <p>p2_pfd_hgh_impdnc=1 ,<br/> p2_pfd_mode[1:0]=01, CP 为测试模式, UP=0, DN=0, UP 电流开启, 测试 UP 电流;</p> <p>p2_pfd_hgh_impdnc=1 ,<br/> p2_pfd_mode[1:0]=10, CP 为测试模式, UP=1, DN=1, DN 电流开启, 测试 DN 电流;</p> <p>p2_pfd_hgh_impdnc=1 ,<br/> p2_pfd_mode[1:0]=11, CP 为高阻模式, UP=1, DN=0, UP 和 DN 电流都关闭;</p> |

|                    | 1:0  | Reserved                      | 2' b0   | RO     |                                                                                                                                                                                                                                                                                             |

| PFD_CTRL           |      |                               |         |        |                                                                                                                                                                                                                                                                                             |

| 0x020              | 7:4  | pfd_dead_delay_bias25u_c[3:0] | 4' h8   | RW     | ZTC 电流, IPfdDeadDelayBias25u =3.25uA*<br>pfd_dead_delay_bias25u_c[3:0]                                                                                                                                                                                                                      |

|                    | 3:2  | pfd_dead_delay[1:0]           | 2' b0   | RW     | <p>Pfd 的 DeadDelay 控制。</p> <p>1) 为&lt;00&gt;和&lt;11&gt;时, DeadDelay 为 2.9ns; &lt;01&gt;时, &lt;00&gt;时, DeadDelay 为 1.3ns; 这两种延迟时间都是用反相器延迟实现的。</p> <p>2) 为&lt;10&gt;时, DeadDelay 为 6ns; 这个延迟时间是用电流的大小控制的, 其中电流受 pfd_dead_delay_bias25u_c[3:0] 控制, 如上。</p>                                    |

|                    | 1:0  | Reserved                      | 2' b0   | RO     |                                                                                                                                                                                                                                                                                             |

| LDT_CTRL           |      |                               |         |        |                                                                                                                                                                                                                                                                                             |

| 0x021              | 7:4  | ldt_cur_bias25u_d[3:0]        | 4' h7   | RW     | ZTC 电流, ILdtCurBias=3.25uA*<br>ldt_cur_bias25u_d[3:0];<br>lockwindow/ unlockwindow 可以通过 ldt_cur_bias25u_d[3:0] 微调                                                                                                                                                                           |

|                    | 3:0  | Reserved                      | 4' b0   | RO     |                                                                                                                                                                                                                                                                                             |

| ALC_TEMP_CUR_CTRL1 |      |                               |         |        |                                                                                                                                                                                                                                                                                             |

| 0x022              | 7    | enn alc temp cur              | 1' b1   | RW     | <p>校准电压的温度特性控制</p> <p>1) 为 0 时, ALC_VTUNE 模块中的 I70 模块输出电流为可配置斜率的负温系数的电流;</p> <p>2) 为 1 时, ALC_VTUNE 模块中的 I70 模块输出电流为可配置大小的零温系数的电流;</p>                                                                                                                                                      |

|                    |      |                               |         |        |                                                                                                                                                                                                                                                                                             |

| Address              | Bits | Register Name                       | Default | Access | Descriptions                                                                                                                                                                                                                               |

|----------------------|------|-------------------------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 6:4  | alc_temp_cur_slope[2:0]             | 3' b0   | RW     | IBIAS_TCF_Temp 模块配置输出电流大小或配置输出电流负温斜率 1)<br>enn_alc_temp_cur=0 时, IOUT 为负温系数; IOUT=200u+<br>alc_temp_cur_slope[2:0]*deltaI2)<br>enn_alc_temp_cur=1 时, IOUT 为零温系数; IOUT=150u+<br>alc_temp_cur_slope[2:0]*50uA                                |

|                      | 3:2  | alc_temp_cali_vol_sel[1:0]          | 2' b0   | RW     | 开环校准电压 ALC 输出选择控制, 由 SPI 控制 (选择 ALc 电压的温度特性: ZTC, PTC, NTC)<br>1)alc_temp_cali_vol_sel[1:0]=00<br>or 01 输出电压为零温电压 ZTC<br>(default: 00)<br>2)alc_temp_cali_vol_sel[1:0]=10<br>输出电压为负温系数电压<br>3)alc_temp_cali_vol_sel[1:0]=11<br>输出电压为正温系数电压 |

|                      | 1:0  | Reserved                            | 2' b0   | RO     |                                                                                                                                                                                                                                            |

| ALC_CALI_REF_VOL     |      |                                     |         |        |                                                                                                                                                                                                                                            |

| 0x023                | 7:4  | Reserved                            | 4' b0   | RO     |                                                                                                                                                                                                                                            |

|                      | 3:0  | alc_cali_ref_vol[3:0]               | 4' h8   | RW     | 校准电压大小控制                                                                                                                                                                                                                                   |

| P1_VCO_BIAS_CUR_CTRL |      |                                     |         |        |                                                                                                                                                                                                                                            |

| 0x024                | 7    | p1_enn_vco_bias_ptat_curent         | 1' b1   | RW     | enn_vco_bias_ptat_curent=0,<br>enable ptat;<br>enn_vco_bias_ptat_curent=1, disable ptat;                                                                                                                                                   |

|                      | 6:4  | p1_vco_bias_current_source[2:0]     | 3' h5   | RW     | VCO 的尾电流偏置源                                                                                                                                                                                                                                |

|                      | 3:2  | p1_vco_bias_ptat_current_slope[1:0] | 2' b0   | RW     |                                                                                                                                                                                                                                            |

|                      | 1    | p1_enn_vco_bias_filter              | 1' b0   | RW     | VCO 偏置的滤波控制, 为 1 时, 关闭滤波; 为 0 时打开滤波。注意仿真时打开滤波 VCO 相噪优化明显。                                                                                                                                                                                  |

|                      | 0    | Reserved                            | 1' b0   | RO     |                                                                                                                                                                                                                                            |

| P2_VCO_BIAS_CUR_CTRL |      |                                     |         |        |                                                                                                                                                                                                                                            |

| 0x025                | 7    | p2_enn_vco_bias_ptat_curent         | 1' b1   | RW     | enn_vco_bias_ptat_curent=0,<br>enable ptat;<br>enn_vco_bias_ptat_curent=1, disable ptat;                                                                                                                                                   |

| Address | Bits                   | Register Name                        | Default | Access | Descriptions                                                                   |

|---------|------------------------|--------------------------------------|---------|--------|--------------------------------------------------------------------------------|

| 0x026   | 6:4                    | p2_vco_bias_cu_rrent_source[2:0]     | 3' h5   | RW     | VCO 的尾电流偏置源                                                                    |

|         | 3:2                    | p2_vco_bias_pstat_current_slope[1:0] | 2' b0   | RW     |                                                                                |

|         | 1                      | p2_en_n_vco_bias_filter              | 1' b0   | RW     | VCO 偏置的滤波控制, 为 1 时, 关闭滤波; 为 0 时打开滤波。注意仿真时打开滤波 VCO 相噪优化明显。                      |

|         | 0                      | Reserved                             | 1' b0   | RO     |                                                                                |

| 0x027   | P1_VCO_BIAS_FILTER_RES |                                      |         |        |                                                                                |

|         | 7:4                    | Reserved                             | 4' b0   | RO     |                                                                                |

|         | 3:0                    | p1_vco_bias_filter_res[3:0]          | 4' b0   | RW     | VCObias 的 RC 电阻配置。                                                             |

| 0x028   | P2_VCO_BIAS_FILTER_RES |                                      |         |        |                                                                                |

|         | 7:4                    | Reserved                             | 4' b0   | RO     |                                                                                |

|         | 3:0                    | p2_vco_bias_filter_res[3:0]          | 4' b0   | RW     | VCObias 的 RC 电阻配置。                                                             |

|         | P1_VCO_TMPE_COMP1      |                                      |         |        |                                                                                |

| 0x029   | 7                      | p1_vco_temp_comp_en                  | 1' b0   | RW     | path1 温度补偿使能, 0 时, enable; 1 时, disable                                        |

|         | 6                      | p1_vco_temp_comp_bias_filter_en      | 1' b0   | RW     | path1 温度补偿滤波电路使能, 0 时, enable; 1 时, disable                                    |

|         | 5                      | p1_sel_vct_temp_p_posneg             | 1' b1   | RW     | 为 1 时, VCT_temp 温度系数为正。为 0 时, VCT_temp 温度系数为负                                  |

|         | 4:0                    | p1_vco_temp_comp_amp[4:0]            | 5' h8   | RW     | VCT_TEMP 的中心值的控制。改变这个控制字时, 可以整体上移或下移动。另外 VcoTempCompAmp<3:0>的取值分别 1, 2、4、8、16。 |

| 0x02A   | P1_VCO_TMPE_COMP2      |                                      |         |        |                                                                                |

|         | 7                      | Reserved                             | 1' b0   | RO     |                                                                                |

|         | 6:4                    | p1_vco_temp_comp_current_slope[2:0]  | 3' h7   | RW     | VCT_temp 时输出温度系数的斜率控制, 值越大, 斜率越大                                               |

|         | 3                      | Reserved                             | 1' b0   | RO     |                                                                                |

| 0x02B   | P1_VCO_TMPE_COMP3      |                                      |         |        |                                                                                |

|         | 7:3                    | Reserved                             | 5' h0   | RO     |                                                                                |

|         | 2:0                    | p1_vco_varactor_temp_comp[2:0]       | 3' b0   | RW     | 用于 VCO 频率温度补偿的 varactor 配置                                                     |

| Address | Bits              | Register Name                       | Default | Access | Descriptions                                                                      |

|---------|-------------------|-------------------------------------|---------|--------|-----------------------------------------------------------------------------------|

| 0x02B   | P2_VCO_TMPE_COMP1 |                                     |         |        |                                                                                   |

|         | 7                 | p2_vco_temp_comp_en                 | 1'b0    | RW     | path2 温度补偿使能, 0 时, enable; 1 时, disable                                           |

|         | 6                 | p2_vco_temp_comp_bias_fiter_en      | 1'b0    | RW     | path2 温度补偿滤波电路使能, 0 时, enable; 1 时, disable                                       |

|         | 5                 | p2_sel_vct_temp_posneg              | 1'b1    | RW     | 为 1 时, VCT_temp 温度系数为正。为 0 时, VCT_temp 温度系数为负                                     |

|         | 4:0               | p2_vco_temp_comp_amp[4:0]           | 5'h8    | RW     | VCT_TEMP 的中心值的控制。改变这个控制字时, 可以整体上移或下移动。另外 VcoTempCompAmp<3:0>的取值分别 1, 2, 4, 8, 16。 |

| 0x02C   | P2_VCO_TMPE_COMP2 |                                     |         |        |                                                                                   |

|         | 7                 | Reserved                            | 1'b0    | RO     |                                                                                   |

|         | 6:4               | p2_vco_temp_comp_current_slope[2:0] | 3'h7    | RW     | VCT_temp 时输出温度系数的斜率控制, 值越大, 斜率越大                                                  |

|         | 3                 | Reserved                            | 1'b0    | RO     |                                                                                   |

|         | 2:0               | p2_vco_varactor_temp_comp[2:0]      | 3'b0    | RW     | 用于 VCO 频率温度补偿的 varactor 配置                                                        |

| 0x02D   | P2_VCO_TMPE_COMP3 |                                     |         |        |                                                                                   |

|         | 7:3               | Reserved                            | 5'h0    | RO     |                                                                                   |

|         | 2:0               | p2_vco_varactor[2:0]                | 3'b0    | RW     | 用于 VCO KV 的配置                                                                     |

| 0x02E   | P1_COMP_CTRL      |                                     |         |        |                                                                                   |

|         | 7                 | p1_en_compare_vct                   | 1'b1    | RW     | 0, disable RFPLL_COMP; 1, enable RFPLL_COM。这个模块的作用是判段控制电压有没在要求的给定的的范围内。           |

|         | 6:4               | p1_compare_ref_h[2:0]               | 3'h1    | RW     | 设置锁定电压的的窗口, 默认为 1. 279<VCT<1. 728。                                                |

|         | 3:1               | p1_compare_ref_l[2:0]               | 3'h6    | RW     |                                                                                   |

|         | 0                 | Reserved                            | 1'b0    | RO     |                                                                                   |

| 0x02F   | P2_COMP_CTRL      |                                     |         |        |                                                                                   |

|         | 7                 | p2_en_compare_vct                   | 1'b1    | RW     | 0, disable RFPLL_COMP; 1, enable RFPLL_COM。这个模块的作用是判段控制电压有没在要求的给定的的范围内。           |

|         | 6:4               | p2_compare_ref_h[2:0]               | 3'h1    | RW     | 设置锁定电压的的窗口, 默认为 1. 279<VCT<1. 728。                                                |

| Address | Bits         | Register Name           | Default | Access | Descriptions       |

|---------|--------------|-------------------------|---------|--------|--------------------|

| 0x030   | 3:1          | p2_compare_ref_1[2:0]   | 3' h6   | RW     |                    |

|         | 0            | Reserved                | 1' b0   | RO     |                    |

| 0x030   | TEST         |                         |         |        |                    |

|         | 7            | en_testclk              | 1' b0   | RW     |                    |

|         | 6            | test_sig_ana_en         | 1' b0   | RW     |                    |

|         | 5            | sel_test_sig_ana        | 1' b0   | RW     |                    |

|         | 4            | test_sig_dig_en         | 1' b0   | RW     |                    |

|         | 3:0          | test_ctrl[3:0]          | 4' b0   | RW     | 测试控制字              |

| 0x031   | TBD          |                         |         |        |                    |

|         | 7:5          | Reserved                | 3' b0   | RO     |                    |

|         | 4            | ldorefilterenn          | 1' b1   | RW     | LDO 参考输入的 RC 滤波    |

|         | 3            | sel_test_cpbk_vcobias   | 1' b0   | RW     |                    |

|         | 2            | en_vct_acloltage        | 1' b0   | RW     |                    |

|         | 1            | sel_test_vco_sel_cmpout | 1' b0   | RW     |                    |

|         | 0            | ldo_ref1p2Sel           | 1' b0   | RW     |                    |

| 0x032   | TBD1         |                         |         |        |                    |

|         | 7:3          | Reserved                | 5' h0   | RO     |                    |

|         | 2:0          | ldo_ref_config[2:0]     | 3' h2   | RW     | Ldoref 的电电阻分压配置。   |

| 0x040   | MIX          |                         |         |        |                    |

|         | MIX_CTRL_COM |                         |         |        |                    |

|         | 7            | Reserved                | 1' b0   | RO     |                    |

|         | 6:4          | pllout_load[2:0]        | 3' h7   | RW     |                    |

|         | 3            | en_pllout               | 1' b0   | RW     |                    |

|         | 2:1          | mixbiastestcon[1:0]     | 2' b0   | RW     | Mixer1/mix2 偏置测试配置 |

| 0x041   | P1_MIX_CTRL1 |                         |         |        |                    |

|         | 7            | p1_bypass_mix           | 1' b0   | RW     |                    |

|         | 6:4          | p1_mix_driver_load[2:0] | 3' h7   | RW     |                    |

| Address | Bits | Register Name                  | Default | Access | Descriptions |

|---------|------|--------------------------------|---------|--------|--------------|

| 0x042   | 3:0  | p1_mixer_dc_ct<br>rl[3:0]      | 4' h8   | RW     |              |

|         | 7    | Reserved                       | 1' b0   | RO     | P1_MIX_CTRL2 |

|         | 6:4  | p1_mix_ibis_ct<br>rl[2:0]      | 3' h4   | RW     |              |

|         | 3:0  | p1_mix_ibis_ct<br>rl_temp[3:0] | 4' h8   | RW     |              |

| 0x043   | 7:4  | p1_mix_lo_dc_c<br>trl[3:0]     | 4' h8   | RW     | P1_MIX_CTRL3 |

|         | 3:0  | p1_mix_trim_ct<br>rl[3:0]      | 4' h8   | RW     |              |

|         | 7    | p2_bypass_mix                  | 1' b0   | RW     | P2_MIX_CTRL1 |

| 0x044   | 6:4  | p2_mix_driver_load[2:0]        | 3' h7   | RW     |              |

|         | 3:0  | p2_mixer_dc_ct<br>rl[3:0]      | 4' h8   | RW     |              |

|         | 7    | Reserved                       | 1' b0   | RO     | P2_MIX_CTRL2 |

| 0x045   | 6:4  | p2_mix_ibis_ct<br>rl[2:0]      | 3' h4   | RW     |              |

|         | 3:0  | p2_mix_ibis_ct<br>rl_temp[3:0] | 4' h8   | RW     |              |

|         | 7:4  | p2_mix_lo_dc_c<br>trl[3:0]     | 4' h8   | RW     | P2_MIX_CTRL3 |

| 0x046   | 3:0  | p2_mix_trim_ct<br>rl[3:0]      | 4' h8   | RW     |              |

|         | 7:0  | extra1_bus[7:0]                | 8' b0   | RW     | EXTRA3       |

| 0x047   | 7:0  | extra2_bus[7:0]                | 8' b0   | RW     | EXTRA4       |

|         | 7:6  | Reserved                       | 2' b0   | RO     | TBD          |

| 0x049   | 5    | enn_filterloin<br>putbias      | 1' b1   | RW     |              |

|         | 4    | enn_filterloin<br>putvcom      | 1' b1   | RW     |              |

|         | 7    | Reserved                       | 2' b0   | RO     |              |

| Address | Bits | Register Name                  | Default | Access | Descriptions |

|---------|------|--------------------------------|---------|--------|--------------|

|         | 3:0  | loinputvcom_cu<br>r[3:0]       | 4' hA   | RW     |              |

| 0x04A   | TBD1 |                                |         |        |              |

|         | 7    | enn_filtervcom<br>uxbias       | 1' b1   | RW     |              |

|         | 6    | enn_filtervcom<br>uxvcom       | 1' b1   | RW     |              |

|         | 5:3  | loinput_bias_c<br>ur[2:0]      | 3' h7   | RW     |              |

|         | 2:0  | loinput_load[2<br>:0]          | 3' h7   | RW     |              |

| 0x04B   | TBD2 |                                |         |        |              |

|         | 7    | Reserved                       | 1' b0   | RO     |              |

|         | 6:3  | vcomuxvcom_cu<br>r[3:0]        | 4' hA   | RW     |              |

|         | 2:0  | vcomux_bias_cu<br>r[2:0]       | 3' h7   | RW     |              |

| 0x04C   | TBD3 |                                |         |        |              |

|         | 7    | Reserved                       | 1' b0   | RO     |              |

|         | 6:4  | vcomux_load[2:<br>0]           | 3' h7   | RW     |              |

|         | 3:0  | Reserved                       | 4' b0   | RO     |              |

| 0x04D   | TBD4 |                                |         |        |              |

|         | 7:4  | Reserved                       | 4' b0   | RO     |              |

|         | 3:0  | refinputvcom_c<br>ur[3:0]      | 4' h8   | RW     |              |

| 0x04E   | TBD5 |                                |         |        |              |

|         | 7    | Reserved                       | 1' b0   | RO     |              |

|         | 6:4  | refinput_bias_c<br>ur[2:0]     | 3' h7   | RW     |              |

|         | 3    | Reserved                       | 1' b0   | RO     |              |

|         | 2:0  | refinput_load[<br>2:0]         | 3' h7   | RW     |              |

| 0x04F   | TBD6 |                                |         |        |              |

|         | 7    | Reserved                       | 1' b0   | RO     |              |

|         | 6:4  | p1_mix_driver<br>bias_cur[2:0] | 3' h7   | RW     |              |

|         | 3:0  | p1_mix_driverv<br>com_cur[3:0] | 4' hA   | RW     |              |

| 0x050   | TBD7 |                                |         |        |              |

|         | 7    | Reserved                       | 1' b0   | RO     |              |

|         | 6:4  | p2_mix_driver<br>bias_cur[2:0] | 3' h7   | RW     |              |